Datasheet

PIC18F2585/2680/4585/4680

DS39625C-page 130 Preliminary © 2007 Microchip Technology Inc.

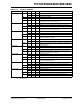

TABLE 10-1: PORTA I/O SUMMARY

Pin Name Function I/O TRIS Buffer Description

RA0/AN0/CV

REF RA0 OUT 0 DIG LATA<0> data output.

IN 1 TTL PORTA<0> data input.

AN0 IN 1 ANA A/D input channel 0. Enabled on POR, this analog input overrides the

digital input (read as clear – low level).

CV

REF OUT x ANA Comparator voltage reference analog output. Enabling this analog

output overrides the digital I/O (read as clear – low level).

RA1/AN1 RA1 OUT 0 DIG LATA<1> data output.

IN 1 TTL PORTA<1> data input.

AN1 IN 1 ANA A/D input channel 1. Enabled on POR, this analog input overrides the

digital input (read as clear – low level).

RA2/AN2/V

REF-RA2 OUT0 DIG LATA<2> data output.

IN 1 TTL PORTA<2> data input.

AN2 IN 1 ANA A/D input channel 2. Enabled on POR, this analog input overrides the

digital input (read as clear – low level).

V

REF-IN1 ANA A/D and comparator negative voltage analog input.

RA3/AN3/V

REF+RA3 OUT0 DIG LATA<3> data output.

IN 1 TTL PORTA<3> data input.

AN3 IN 1 ANA A/D input channel 3. Enabled on POR, this analog input overrides the

digital input (read as clear – low level).

V

REF+IN1 ANA A/D and comparator positive voltage analog input.

RA4/T0CKI RA4 OUT 0 DIG LATA<4> data output.

IN 1 TTL PORTA<4> data input.

T0CKI IN 1 ST Timer0 clock input.

RA5/AN4/SS

/HLVDIN RA5 OUT 0 DIG LATA<5> data output.

IN 1 TTL PORTA<5> data input.

AN4 IN 1 ANA A/D input channel 4. Enabled on POR, this analog input overrides the

digital input (read as clear – low level).

SS

IN 1 TTL Slave select input for MSSP.

HLVDIN IN 1 ANA High/Low-Voltage Detect external trip point input.

OSC2/CLKO/RA6 OSC2 OUT x ANA Output connection, selected by FOSC3:FOSC0 Configuration bits.

Enabling OSC2 overrides digital I/O.

CLKO OUT x DIG Output connection, selected by FOSC3:FOSC0 Configuration bits.

Enabling CLKO overrides digital I/O (F

OSC/4).

RA6 OUT 0 DIG LATA<6> data output.

IN 1 TTL PORTA<6> data input.

OSC1/CLKI/RA7 OSC1 IN x ANA Main oscillator input connection, determined by FOSC3:FOSC0

Configuration bits. Enabling OSC1 overrides digital I/O.

CLKI IN x ANA Main clock input connection, determined by FOSC3:FOSC0

Configuration bits. Enabling CLKI overrides digital I/O.

RA7 OUT 0 DIG LATA<7> data output.

IN 1 TTL PORTA<7> data input.

Legend: PWR = Power Supply; OUT = Output; IN = Input; ANA = Analog Signal; DIG = Digital Output; ST = Schmitt Buffer Input;

TTL = TTL Buffer Input