Information

Table Of Contents

© 2008 Microchip Technology Inc. DS80171L-page 5

PIC16F87/88

8. Module: Oscillator Configurations

(OSCTUNE Register)

The Device Data Sheet has been revised to reflect

changes in the operation of the OSCTUNE

register, beginning with silicon Revision C0. The

following text and table describe that register’s

implementation for silicon Revision B1.

The OSCTUNE register adjusts the frequencies of

the INTOSC and INTRC clock sources.

OSCTUNE bit 0 is implemented. When the register

is modified, the INTOSC and INTRC frequencies

begin shifting to the new frequency. The INTRC

clock reaches the new frequency within eight clock

cycles (approximately 8 * 32 μs or 256 μs).

Work around

N/A

Date Codes that pertain to this issue:

All date codes associated with silicon revision B1.

This issue is not found in devices with silicon

revision C2 (Revision ID 0 1000) or later.

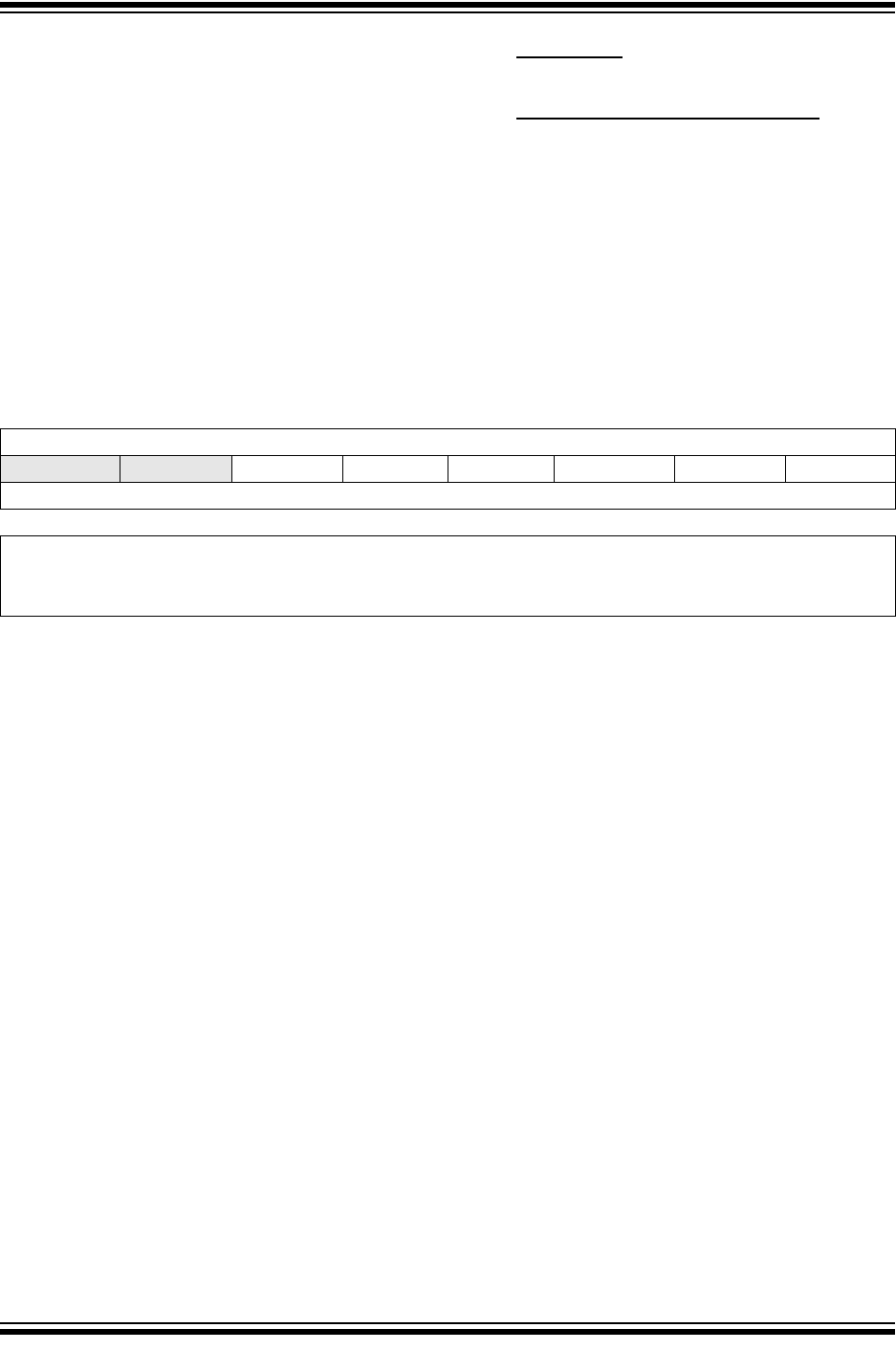

REGISTER 4-1: OSCTUNE: OSCILLATOR TUNING REGISTER (ADDRESS 90h)

U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

— — TUN5 TUN4 TUN3 TUN2 TUN1 TUN0

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 7-6 Unimplemented: Read as ‘0’

bit 5-0 TUN<5:0>: Frequency Tuning bits

011111 = Maximum frequency

011110 =

•

•

•

000001 =

000000 = Center frequency. Oscillator module is running at the calibrated frequency.

111111 =

•

•

•

100000 = Minimum frequency