Datasheet

Table Of Contents

- MCP3905A/05L/06A

- Features

- Description

- Package Type

- Functional Block Diagram

- Notes:

- 1.0 Electrical Characteristics

- 2.0 Typical Performance Curves

- FIGURE 2-1: Measurement Error, Gain = 8 PF = 1.

- FIGURE 2-2: Measurement Error, Gain = 16, PF = 1.

- FIGURE 2-3: Measurement Error, Gain = 32, PF = 1.

- FIGURE 2-4: Measurement Error, Gain = 8, PF = 0.5.

- FIGURE 2-5: Measurement Error, Gain = 16, PF = 0.5.

- FIGURE 2-6: Measurement Error, Gain =32, PF = 0.5.

- FIGURE 2-7: Measurement Error, Gain = 1, PF = 1.

- FIGURE 2-8: Measurement Error, Gain = 2, PF = 1.

- FIGURE 2-9: Measurement Error, Gain = 1, PF = + 0.5.

- FIGURE 2-10: Measurement Error, Gain = 2, PF = + 0.5.

- FIGURE 2-11: Measurement Error, Temperature = +125°C, Gain = 1.

- FIGURE 2-12: Measurement Error, Temperature = +125°C, Gain = 2.

- FIGURE 2-13: Measurement Error, Temperature = +125°C, Gain = 8.

- FIGURE 2-14: Measurement Error, Temperature = +125°C, Gain = 16.

- FIGURE 2-15: Measurement Error vs. Input Frequency.

- FIGURE 2-16: Channel 0 Offset Error (DC Mode, HPF off), G = 1.

- FIGURE 2-17: Channel 0 Offset Error (DC Mode, HPF off), G = 8.

- FIGURE 2-18: Channel 0 Offset Error (DC Mode, HPF Off), G = 16.

- FIGURE 2-19: Measurement Error vs. VDD (G = 16).

- FIGURE 2-20: Measurement Error vs. VDD, G = 16, External VREF.

- FIGURE 2-21: Measurement Error w/ External VREF, (G = 1).

- FIGURE 2-22: Measurement Error w/ External VREF (G = 8).

- FIGURE 2-23: Measurement Error w/ External VREF (G = 16).

- 3.0 Pin Descriptions

- TABLE 3-1: Pin Function Table

- 3.1 Digital VDD (DVDD)

- 3.2 High-Pass Filter Input Logic Pin (HPF)

- 3.3 Analog VDD (AVDD)

- 3.4 Current Channel (CH0-, CH0+)

- 3.5 Voltage Channel (CH1-,CH1+)

- 3.6 Master Clear (MCLR)

- 3.7 Reference (REFIN/OUT)

- 3.8 Analog Ground (AGND)

- 3.9 Frequency Control Logic Pins (F2, F1, F0)

- 3.10 Gain Control Logic Pins (G1, G0)

- 3.11 Oscillator (OSC1, OSC2)

- 3.12 Negative Power Output Logic Pin (NEG)

- 3.13 Ground Connection (DGND)

- 3.14 High-Frequency Output (HFOUT)

- 3.15 Frequency Output (FOUT0, FOUT1)

- 4.0 Device Overview

- 5.0 Applications Information

- 6.0 Packaging Information

- Trademarks

- Worldwide Sales and Service

© 2006-2011 Microchip Technology Inc. DS22011B-page 3

MCP3905A/05L/06A

1.0 ELECTRICAL

CHARACTERISTICS

Absolute Maximum Ratings †

V

DD

...................................................................................7.0V

Digital inputs and outputs w.r.t. A

GND

........ -0.6V to V

DD

+0.6V

Analog input w.r.t. A

GND

.........................................-6V to +6V

V

REF

input w.r.t. A

GND

............................... -0.6V to V

DD

+0.6V

Storage temperature .....................................-65°C to +150°C

Ambient temp. with power applied................-65°C to +125°C

Soldering temperature of leads (10 seconds) .............+300°C

ESD on the analog inputs (HBM,MM).................5.0 kV, 500V

ESD on all other pins (HBM,MM)........................5.0 kV, 500V

† Notice: Stresses above those listed under “Maximum

Ratings” may cause permanent damage to the device.

This is a stress rating only and functional operation of

the device at those or any other conditions above those

indicated in the operation listings of this specification is

not implied. Exposure to maximum rating conditions for

extended periods may affect device reliability.

ELECTRICAL CHARACTERISTICS

Electrical Specifications: Unless otherwise indicated, all parameters apply at AV

DD

= DV

DD

= 4.5V – 5.5V,

Internal V

REF

, HPF turned on (AC mode), A

GND

, D

GND

= 0V, MCLK = 3.58 MHz; T

A

= -40°C to +85°C.

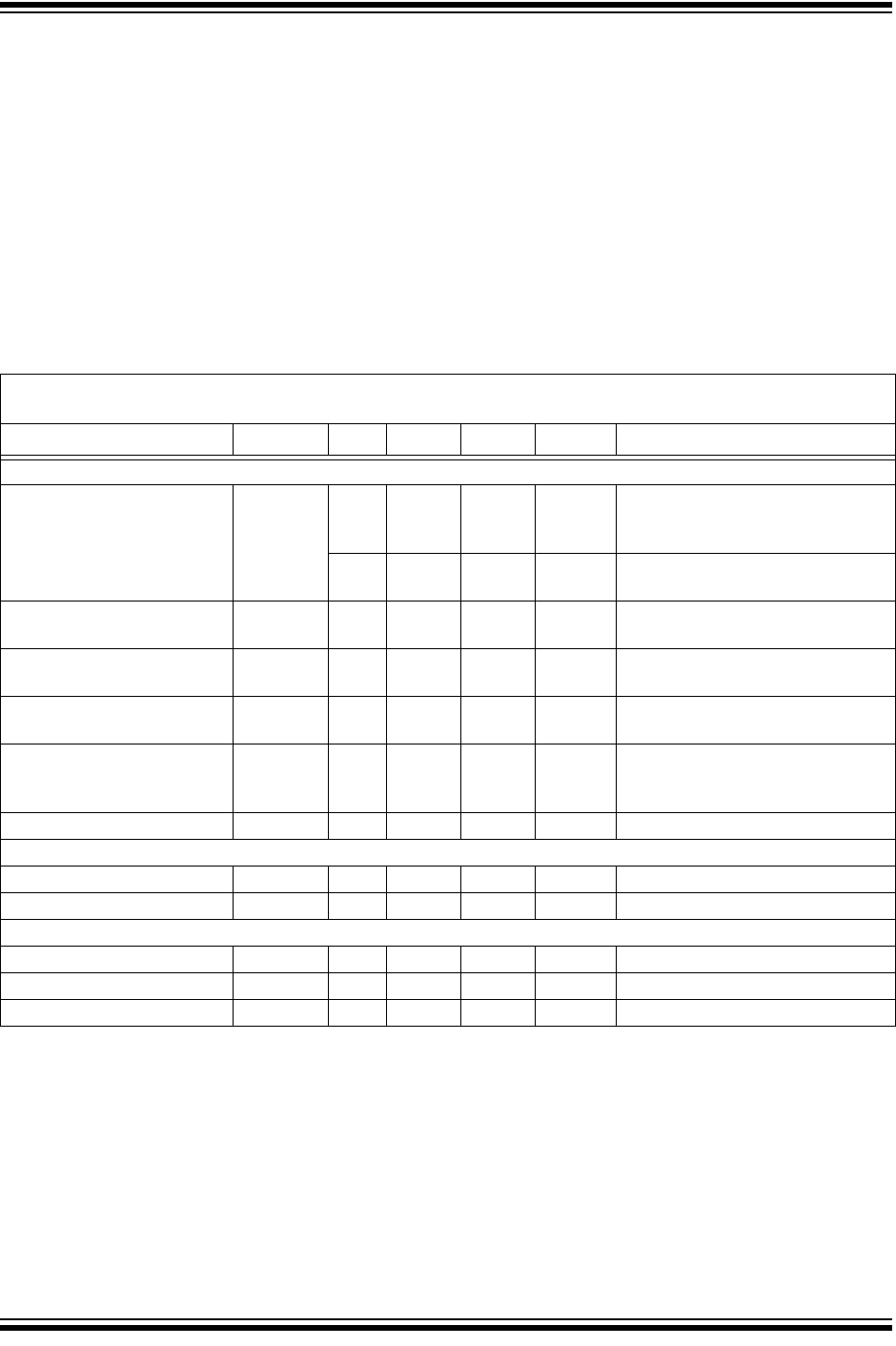

Parameter Sym Min Typ Max Units Comment

Overall Measurement Accuracy

Energy Measurement Error E — 0.1 — % F

OUT

Channel 0 swings 1:500 range,

MCP3905A, MCP3905L only

(Note 1, Note 4)

— 0.1 — % F

OUT

Channel 0 swings 1:1000 range,

MCP3906A only (Note 1, Note 4)

No-Load Threshold/

Minimum Load

NLT — 0.0015 — % F

OUT

Max

Disabled when F2, F1, F0 = 0, 1, 1

(Note 5, Note 6)

Phase Delay Between

Channels

— — 1/MCLK s HPF = 0 and 1, < 1 MCLK

(Note 4, Note 6, Note 7)

AC Power Supply Rejection

(output frequency variation)

AC PSRR — 0.01 — % F

OUT

F2, F1, F0 = 0, 1, 1 (Note 3)

DC Power Supply Rejection

(output frequency

variation)

DC PSRR — 0.01 — % F

OUT

HPF = 1, Gain = 1 (Note 3)

System Gain Error — 3 10 % F

OUT

(Note 2, Note 5)

ADC/PGA Specifications

Offset Error V

OS

— 2 5 mV Referred to Input

Gain Error Match — 0.5 — % F

OUT

(Note 5)

Internal Voltage Reference

Voltage — 2.4 — V

Tole ranc e — ±2 — %

Tempco — 15 — ppm/°C

Note 1: Measurement error = (Energy Measured By Device - True Energy)/True Energy * 100%. Accuracy is

measured with signal (±660 mV) on Channel 1. F

OUT0

, F

OUT1

pulse outputs. Valid from 45 Hz to 65 Hz.

See typical performance curves for higher frequencies and increased dynamic range.

2: Does not include internal V

REF

. Gain = 1, CH0 = 470 mVDC, CH1 = 660 mVDC, difference between

measured output frequency and expected transfer function.

3: Percent of HF

OUT

output frequency variation; Includes external V

REF

= 2.5V, CH1 = 100 mVRMS @

50 Hz, CH2 = 100 mVRMS @ 50 Hz, AV

DD

= 5V + 1V

pp

@ 100 Hz. DC PSRR: 5V ±500 mV

4: Error applies down to 60 degree lead (PF = 0.5 capacitive) and 60 degree lag (PF = 0.5 inductive).

5: Refer to Section 4.0 “Device Overview” for complete description.

6: Specified by characterization, not production tested.

7: 1 MCLK period at 3.58 MHz is equivalent to less than <0.005 degrees at 50 or 60 Hz.