Information

Table Of Contents

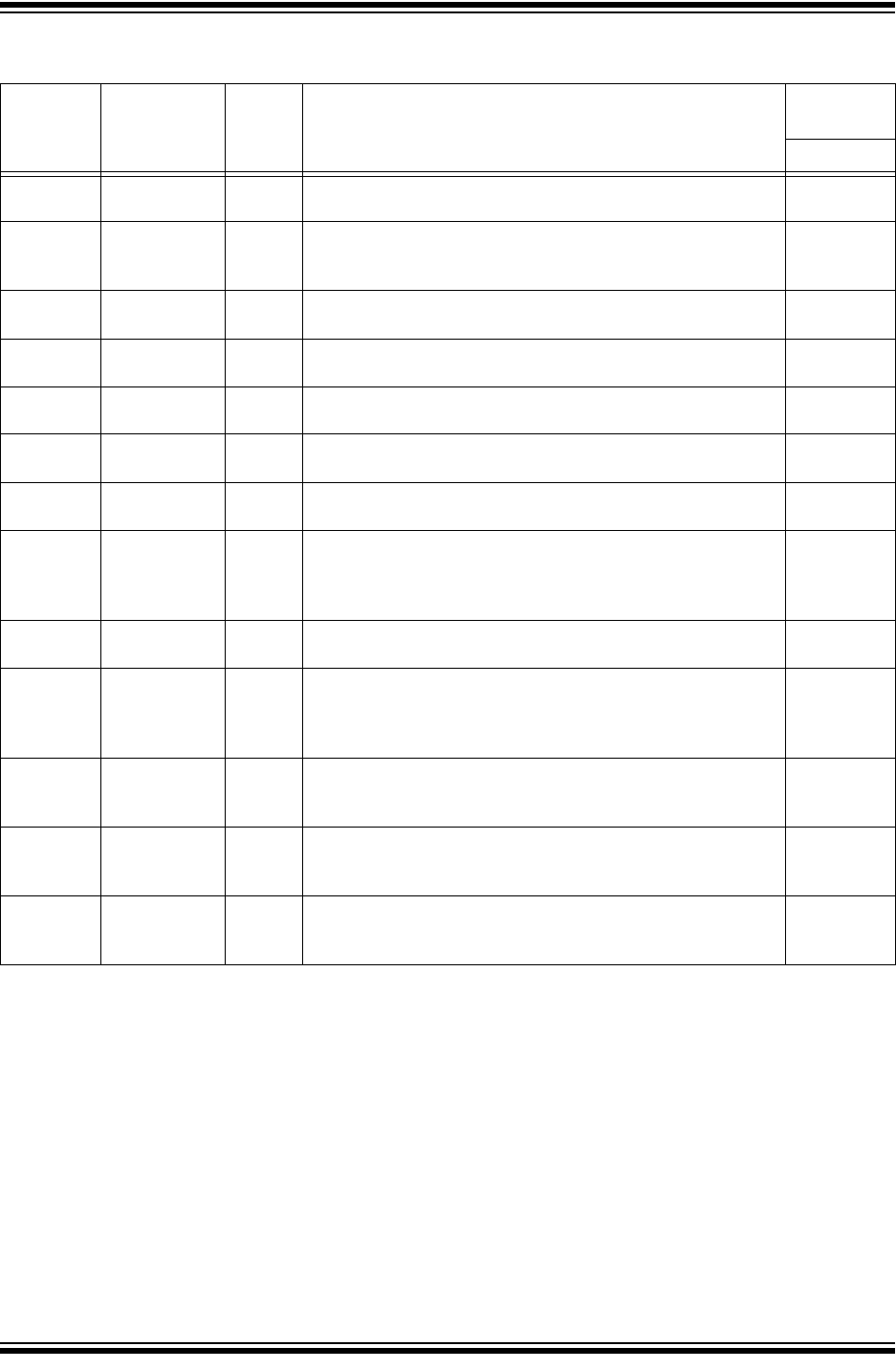

- TABLE 1: Silicon DEVREV Values (Continued)

- TABLE 2: Silicon Issue Summary (Continued)

- Silicon Errata Issues

- 1. Module: I/O Multiplexer

- 2. Module: CPU

- 3. Module: CPU

- 4. Module: PPS

- 5. Module: SPI

- 6. Module: SPI

- 7. Module: PWM

- 8. Module: PWM

- 9. Module: Power System

- 10. Module: Reserved

- 11. Module: ECAN™

- 12. Module: ECAN

- 13. Module: USB

- 14. Module: USB

- 15. Module: DMA

- 16. Module: UART

- 17. Module: UART

- 18. Module: UART

- 19. Module: I2C™

- 20. Module: ADC

- 21. Module: PMP

- 22. Module: Flash Memory

- 23. Module: Flash Memory

- 24. Module: Power System

- 25. Module: PWM

- 26. Module: QEI

- 27. Module: QEI

- 28. Module: CPU

- 29. Module: PWM

- 30. Module: ECAN

- 31. Module: Auxiliary Flash

- 32. Module: Auxiliary Flash

- 33. Module: Output Compare

- 34. Module: ADC

- Data Sheet Clarifications

- Appendix A: Revision History

dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

DS80526C-page 4 © 2011-2012 Microchip Technology Inc.

Flash

Memory

ICSP™ 22. If either the General or Auxiliary Segment is protected, neither

segment can be read.

X

Flash

Memory

Programming 23. Stall mechanism may not function properly when erasing or

programming Flash memory while executing code from the

same Flash segment.

X

Power

System

Flash

Regulator

24. The RCON<VREGSF> bit always reads as ‘0’. X

PWM Dead Time 25. When operating in Edge-Aligned Complimentary mode the

dead time could become zero.

X

QEI Index Counter 26. The QEI Index Counter does not count correctly in Quadrature

Detector mode.

X

QEI Modulo Mode 27. Modulo mode functionality is incorrect when the Count Polarity

bit is set.

X

CPU DO Loop 28. PSV access, including table reads or writes, in the last

instruction of a DO loop are not allowed.

X

PWM Master Time

Base Mode

29. In Master Time Base mode, writing to the period register and

any other timing parameter of the PWM module will cause the

update of the other timing parameter to take effect one PWM

cycle after the period update is effective.

X

ECAN DMA 30. Write collisions on DMA enabled ECAN peripheral do not

generate DMAC Error traps.

X

Auxiliary

Flash

Interrupt

Vector

31. When a device is set to obtain the reset instruction from

Auxiliary Flash location 0x7FFFFC (RSTPRI = 0) and Auxiliary

Flash code protection is enabled, the device does not execute

the application code after a Reset.

X

Auxiliary

Flash

Interrupt

Vector

32. All interrupts and traps should vector through the single

auxiliary interrupt vector when executing from the Auxiliary

Segment; however, the Address Error trap is not.

X

Output

Compare

Interrupt 33. Under certain circumstances, an Output Compare match may

cause the interrupt flag (OCxIF) to become set prior to the

change of state of the OCx pin.

X

ADC

1.1 Msps

Sampling

34.

Selecting the same ANx input (AN0 or AN3) for CH0 and CH1

to achieve a 1.1 Msps sampling rate results in erroneous

readings for CH1.

X

TABLE 2: SILICON ISSUE SUMMARY (CONTINUED)

Module Feature

Item

Number

Issue Summary

Affected

Revisions

(1)

B1

Note 1: Only those issues indicated in the last column apply to the current silicon revision.