Information

Table Of Contents

- TABLE 1: Silicon DEVREV Values (Continued)

- TABLE 2: Silicon Issue Summary (Continued)

- Silicon Errata Issues

- 1. Module: I/O Multiplexer

- 2. Module: CPU

- 3. Module: CPU

- 4. Module: PPS

- 5. Module: SPI

- 6. Module: SPI

- 7. Module: PWM

- 8. Module: PWM

- 9. Module: Power System

- 10. Module: Reserved

- 11. Module: ECAN™

- 12. Module: ECAN

- 13. Module: USB

- 14. Module: USB

- 15. Module: DMA

- 16. Module: UART

- 17. Module: UART

- 18. Module: UART

- 19. Module: I2C™

- 20. Module: ADC

- 21. Module: PMP

- 22. Module: Flash Memory

- 23. Module: Flash Memory

- 24. Module: Power System

- 25. Module: PWM

- 26. Module: QEI

- 27. Module: QEI

- 28. Module: CPU

- 29. Module: PWM

- 30. Module: ECAN

- 31. Module: Auxiliary Flash

- 32. Module: Auxiliary Flash

- 33. Module: Output Compare

- 34. Module: ADC

- Data Sheet Clarifications

- Appendix A: Revision History

© 2011-2012 Microchip Technology Inc. DS80526C-page 3

dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

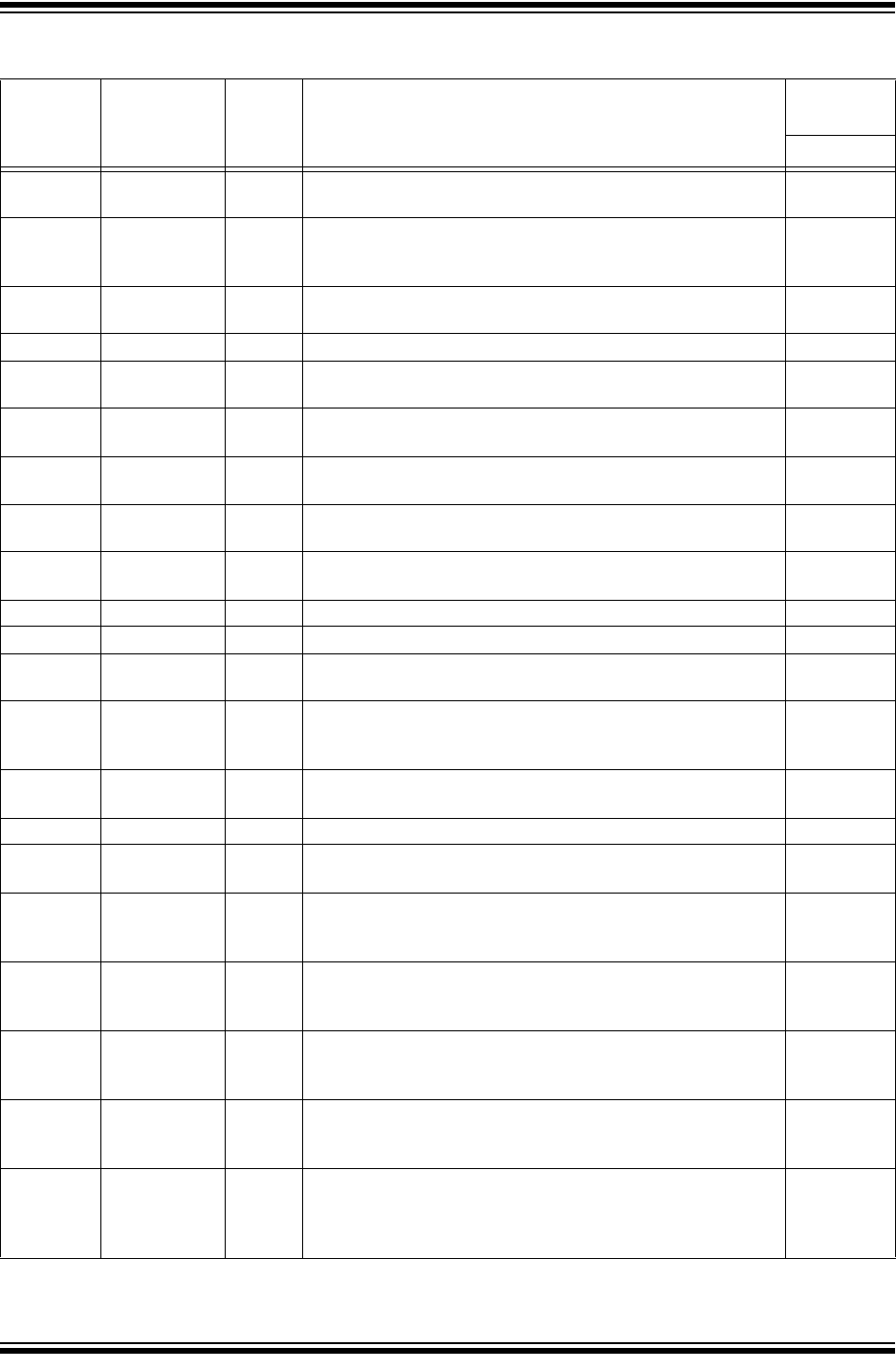

TABLE 2: SILICON ISSUE SUMMARY

Module Feature

Item

Number

Issue Summary

Affected

Revisions

(1)

B1

I/O

Multiplexer

Open Drain

Feature

1. The open drain control signal from GPIO, PORTA bit 3, is

inadvertently controlling the data output of bit 15 of PORTC.

X

CPU DSP DO

Instruction

2. The assembly language DO instruction does not function

correctly with nested loops when the inner loop count is zero

(one iteration).

X

CPU div.sd

Instruction

3. When using the div.sd instruction, the overflow bit is not

getting set when an overflow occurs.

X

PPS Virtual Remap 4. Virtual pin remapping does not work correctly. X

SPI Frame Sync

Pulse

5. Frame sync pulse not generated in Master mode when

FRMPOL = 0.

X

SPI Frame Sync

Pulse

6. When in SPI Slave mode, with the frame sync pulse set as an

input, FRMDLY must be set to ‘0’.

X

PWM Dead Time

Compensation

7. The duty cycle is not correct when using dead time and the

programmed duty cycle is close to 0% or 100%.

X

PWM Dead Time

Compensation

8. Dead Time Compensation is not enabled for Center Aligned

PWM Mode.

X

Power

System

BOR 9. BOR must always be enabled. X

Reserved — 10. ——

ECAN™ CANCKS 11. The function of the CANCKS bit is reversed. X

ECAN ERRIF 12. The ERRIF status bit does not get set when a CAN error

condition occurs.

X

USB LS through

Hub

13. The USB bus might not be returned to the J-state following an

acknowledgement packet when running low-speed through a

hub.

X

USB UIDLE

Interrupt

14. UIDLE interrupts cease if the UIDLE interrupt flag is cleared. X

DMA CAN

15. Possible loss of interrupts when DMA is used with CAN. X

UART TX Interrupt 16. A TX Interrupt may occur before the data transmission is

complete.

X

UART UTXBRK 17. When a Read-Modify-Write operation is performed to set or

clear any bit(s) in the UxSTA register while hardware is

clearing the UTXBRK bit, the UTXBRK bit may remain set.

X

UART UARTEN 18. The transmitter write pointer does not get cleared when the

UART is disabled (UARTEN = 0), it requires TXEN to be set in

order to clear the write pointer.

X

I

2

C™ I2CxCON 19. When a Read-Modify-Write operation is performed to set or

clear any bit(s) in the I2CxCON register while hardware is

clearing the ACKEN bit, the ACKEN bit may remain set.

X

ADC DONE bit 20. The ADC Conversion Status bit, DONE (ADxCON1<0>), does

not indicate completion of conversion when External Interrupt is

selected as the ADC trigger source (ADxCON1<SSRC> = 1).

X

PMP — 21. On the dsPIC33EPXXXGU814 or PIC2EPXXXMU814

devices, the PMCS1/PMA14 and PMCS2/PMA15 pin

functionality is duplicated on the RJ14/15 pins in addition to

the expected RK11/RK12 pins.

X

Note 1: Only those issues indicated in the last column apply to the current silicon revision.