Datasheet

dsPIC30F1010/202X

DS70178C-page 108 Preliminary © 2006 Microchip Technology Inc.

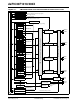

FIGURE 12-1: SIMPLIFIED CONCEPTUAL BLOCK DIAGRAM OF POWER SUPPLY PWM

MUX

Latch

Comparator

Timer

PDC2

Phase

MUX

Latch

Comparator

Timer

PDC3

Phase

MUX

Latch

Comparator

Timer

PDC4

Phase

MUX

Latch

Comparator

Timer

PDC1

PWMCONx

LEBCONx

Channel 1

Dead-time Generator

PTCON

SEVTCMP

Comparator

Special Event

IOCONx

PWM enable and mode control

Channel 3

Dead-time Generator

Channel 4

Dead-time Generator

ALTDTRx, DTRx

Dead-time Control

Special Event

Postscaler

SFLTX

PWM3L

PWM3H

PWM2L

PWM2H

16-bit Data Bus

PWM1L

PWM1H

FLTCONx

Pin and mode control

MDC

ADC Trigger Control

Master Duty Cycle Reg

Fault mode and pin control

Pin override control

Special event

PTPER

Timer Period

PWM GEN #1

PWM GEN #2

PWM GEN #4

PTMR

Master Time Base

Phase

PWM GEN #3

Channel 2

Dead-time Generator

PWM4L

PWM4H

PWM User, Current Limit and Fault Override and Routing Logic

Fault CLMT Override Logic

Trigger

comparison value

IFLTX

Fault Control

Logic

TRGCONx

Control for blanking external input signals

External Time Base

Synchronization

SYNCO

SYNCI