User manual

Board Description

4-6 AT91SAM9M10-G45-EK User Guide

6495B–ATARM–21-Apr-10

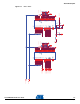

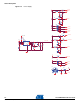

Figure 4-4. EBI1 - DDR2 + Flash

Optional 16bits DATA BUS

With AT29F2G16ABD Micron

(SDA10)

(

SDA10)

(NCS3)

(RDY/BSY

)

(N

AN

DAL

E

)

(N

AN

DCLE)

(NCS1)

I

M

PORTAN

T

note

about

s

ystem

booti

n

g:

The b

oo

tROM

a

llows

booti

ng

fro

m

the b

lo

ck 0

o

f a N

an

dFla

sh

co

nn

ected

on CS3. However, the

bootROM does

not f

e

ature ECC (E

r

ror Checking

and

Corre

c

tion) on NandFlash

.

Most of t

h

e NandFlash

v

endor

s

do no

t

guar

a

ntee a

n

ymore

that block 0

i

s erro

r

free

.

Ther

ef

ore w

e

advi

se

the

b

ootst

ra

p pro

g

ram t

o

be l

oc

ated

into

a

noth

er

devi

ce

sup

po

rted

by

the

b

ootro

m

(Dat

aF

lash

,

Seria

l

Flas

h,

S

DCA

RD o

r

EEPR

OM)

and

i

mple

men

t Na

nd

Flas

h

acce

ss

with

E

CC.

WP

RE

WE

CE

RB EBI1_NAND_FSH_D6

EBI1_NAND_FSH_D0

EBI1_NAND_FSH_D3

EBI1_NAND_FSH_D4

EBI1_NAND_FSH_D2

EBI1_NAND_FSH_D1

EBI1_NAND_FSH_D5

EBI1_NAND_FSH_D7

EBI1_NAND_FSH_D14

EBI1_NAND_FSH_D8

EBI1_NAND_FSH_D11

EBI1_NAND_FSH_D12

EBI1_NAND_FSH_D10

EBI1_NAND_FSH_D9

EBI1_NAND_FSH_D13

EBI1_NAND_FSH_D15

EBI1_DDR_D15

EBI1_D

D

R

_D

11

EBI

1_D

D

R

_D

10

EBI1_D

D

R

_

D12

EBI1_DDR_D8

EBI

1_D

D

R

_D

9

EBI1_DDR_D13

EBI1_DDR_D14

EBI

1_DDR

_

D7

EBI

1_DDR_D3

EBI

1_DDR_D2

EBI

1_DDR

_

D4

EBI

1_DDR_D0

EBI

1_DDR_D1

EBI

1_DDR

_

D5

EBI

1_DDR

_

D6

EBI1_FLASH_D4

EBI1_FLASH_D2

EBI1_FLASH_D10

EBI1_FLASH_D5

EBI1_FLASH_D12

EBI1_F

LASH_D9

EBI1_FLASH_D14

EBI1_FLASH_D15

EBI1_FLASH_D3

EBI1_F

LASH

_D

0

EBI1_FLASH_D6

EBI1_FLASH

_D

7

EBI1_F

LASH

_D

8

EBI

1_FLASH_D1

EBI1_FLASH_D13

EBI1_FLASH_D11

EBI1_DD

R

_A2

EBI1_DDR_A3

EBI1

_

DDR_A4

EBI1

_

DDR_A5

EBI1

_

DDR_A6

EBI1

_

DDR_A7

EBI1

_

DDR_A8

EBI1

_

D

D

R_

A9

EBI1

_

D

D

R_

A1

0

EBI1

_

D

D

R_

A1

1

EBI1

_

D

D

R_

A1

2

EBI1

_

D

D

R_

A1

3

EBI1

_DD

R_

A1

5

EBI1

_

D

D

R_

A1

4

EBI1_

D

DR_A2

EBI1_

D

DR

_

A3

EBI

1

_

D

DR_A4

EBI

1

_DDR

_

A5

E

BI1_

D

DR_A6

EBI1

_

D

DR

_

A7

EB

I1

_

D

D

R_

A8

EBI1_

D

D

R_

A9

EBI

1

_

D

D

R_

A1

0

EBI1_D

D

R_

A1

1

EBI1_D

D

R_

A1

2

EBI1_D

D

R_A13

EBI1_DDR_A15

EBI1_DDR_A14

NCLK_EBI1

CS_EBI1

BA0

_

EBI

1

BA1

_EBI1

RAS_EBI1

CAS_EBI1

W

E_

EBI1

CKE_EBI1

CLK_EBI1

NCL

K_

EBI1

CS_EBI1

BA0_

EBI

1

BA1_EBI1

R

AS_EBI1

C

AS_EBI1

WE_EBI1

C

KE_

EBI1

VREF1

EBI1_F

LASH

_A1

EBI1_FLASH

_A2

EBI1_F

LASH

_A3

EBI1_F

LASH

_A4

EBI1_F

LASH

_A5

EBI1_F

LASH

_A6

EBI1_FLASH_A7

EBI1_FLASH_A8

EBI1_FLASH_A9

EBI1_FLASH_A10

EBI1_FLASH_A11

EBI1_FLASH_A12

EBI1_FLASH_A15

EBI1_FLASH_A14

EBI1_FLASH_A13

EBI1_FLASH_A16

EBI1_FLASH_A18

EBI1_FLASH_A17

VREF1

VREF1

EBI

1_FLASH_A19

EBI

1_FLASH_A20

EBI1_FLASH_A21

CLK_EBI1

1V8

1V8

1V8

1V8

1V8

1V8

1V8

1V8 1V8

EBI1

_

FLASH_D[

0

..15]

BA0_EBI1

PC8

EBI1

_

DD

R

_D

[

0.

.

15]

EBI1

_

FLASH

_

A[1..21]

EBI1

_

D

DR

_

A[2

..

1

5

]

BA1_EBI1

C

KE_

EBI1

C

L

K_

EBI1

NCLK_

EBI1

CS_

EBI1

CAS_

EBI

1

RAS_EBI1

W

E_

EBI1

D

Q

S0

_

EBI1

D

Q

M

0

_

EBI1

DQS1_EBI1

DQM1_EBI1

EBI1_NCS0

EBI1_NRD/CFOE

DDR_VREF

EBI1_NWE/NWR0/CFWE

PC5

PC4

EBI1_NAND

O

E

EBI1_NAND

W

E

PC14

EBI

1_NAND_FSH_D[0..15]

JP9JP9

R43

0R

R43

0R

C81 100nFC81 100nFC

8

0 1

00

nFC

8

0 1

00

nF

MT4

7

H6

4

M8

C

F

-

3

DD

R

2

SD

R

AM

MN8

MT4

7

H6

4

M8

C

F

-

3

DD

R

2

SD

R

AM

MN8

A0

H8

A1

H3

A2

H7

A3

J2

A4

J8

A5

J3

A6

J7

A7

K2

A8

K8

A9

K3

A10

H2

BA0

G

2

ODT

F9

DQ0

C8

DQ1

C2

DQ2

D7

DQ3

D3

DQ

4

D1

DQ

5

D9

DQ

6

B1

DQ

7

B9

D

Q

S

B7

D

Q

S

A8

RD

Q

S/D

M

B3

RDQS/N

U

A2

VD

D

H9

VD

D

L1

VDDL

E1

VRE

F

E2

VDDQ

C9

VSS

A3

VSS

E3

VDDQ

A9

VD

D

E9

R

F

U

1

G

1

R

F

U

2

L3

CKE

F2

CK

E8

CK

F8

C

AS

G7

R

AS

F7

W

E

F3

C

S

G8

VDDQ

C1

VDDQ

C3

VDDQ

C7

VSSQ

B2

VSSQ

B8

VSSQ

D2

VSSQ

D8

VD

D

A1

VSS

J1

A1

1

K7

BA1

G

3

A1

2

L

2

A13

L8

VSS

K9

VSSDL

E7

VSSQ

A7

RFU3

L

7

R40 470KR40 470K

C101

100nF

C101

100nF

C104 100nFC104 100nF

C

8

2 100nFC

8

2 100nF

R46 470KR46 470K

AT49SV32

2

DT

FLAS

H

CBGA

M

N

10

DNP

AT49SV32

2

DT

FLAS

H

CBGA

M

N

10

DNP

A0

E1

A1

D1

A2

C

1

A3

A1

A4

B1

A5

D

2

A6

C2

A7

A2

A8

B5

A9

A5

A10

C5

A11

D5

A12

B6

A13

A6

A14

C6

A15

D6

A16

E6

A17

B2

A18

C3

RDY/ BUSY

A3

A20

D3

A19

D4

WE

A4

RESET

B4

OE

G1

CE

F1

VPP

B3

I

/

00

E2

I

/

O

1

H

2

I

/

O

2

E3

I

/

O

3

H3

I

/

O

4

H4

I/O5

E4

I/O6

H5

I/O7

E5

I/O8

F2

I/O9

G

2

I/O10

F3

I/O11

G3

I/O12

F4

I/O13

G5

I/O14

F5

I/O15

G6

VCC

G4

GND

H6

GND

H1

NC1

C4

NC

F6

R42

0R

R42

0R

R39 100KR39 100K

MT

29F2

G0

8ABD

NAND FL

A

SH

VFBGA-63

MN1

1

MT29F2G08ABDHC:D

MT

29F2

G0

8ABD

NAND FL

A

SH

VFBGA-63

MN1

1

MT29F2G08ABDHC:D

WE

C7

N.C6

B9

VCC

H8

CE

C

6

RE

D4

N

.C

1

1

E3

W

P

C3

N.C5

B1

N.C1

A1

N.C2

A2

N.C3

A9

N.C4

A10

N

.C

1

2

E4

N.C13

E5

N.C14

E6

N.C15

E7

R/B

C8

N.C17

F3

N.C36

M1

I/O0

H4

N.C34

L9

N

.C

2

5

L

2

VSS

F7

N.C29

J5

VCC

J6

VSS

K3

ALE

C4

N

.C8

D6

N.C7

B10

N

.C9

D7

N

.C10

D8

CLE

D5

N.C16

E8

N.C35

L10

I/O1

J4

I/O3

K5

I/O2

K4

N.C28

H5

N.C30

H6

N.C32

H7

I/O7

J8

I/O6

K7

I/O5

J7

I/O4

K6

N.C27

J3

N.C26

H3

VSS

C5

N

.C

2

4

L

1

VSS

K8

L

OCK

G5

VCC

D3

VCC

G4

N.C31

G6

N.C18

F4

N

.C19

F5

N

.C20

F6

N

.C22

G3

N

.C21

F8

N.C33

G7

N

.C23

G8

N.C37

M2

N.C38

M9

N.C39

M10

C87 100nFC87 100nF

JP10JP10

C

9

4 10

0

n

F

C

9

4 10

0

n

F

R

4

5

1

K

R

4

5

1

K

C93 100nFC93 100nF

C83 100nFC83 100nF

R

4

1

470K

R

4

1

470K

MT47H6

4

M8

C

F-3

DD

R

2

S

DRAM

MN9

MT47H6

4

M8

C

F-3

DD

R

2

S

DRAM

MN9

A0

H

8

A1

H

3

A2

H

7

A3

J

2

A4

J8

A5

J3

A6

J7

A7

K2

A8

K8

A9

K3

A10

H2

BA0

G2

O

DT

F9

DQ0

C8

DQ1

C2

DQ2

D7

DQ3

D3

D

Q4

D

1

D

Q5

D

9

D

Q6

B1

D

Q

7

B9

DQS

B7

DQS

A8

RDQS/DM

B3

RDQS/NU

A2

VDD

H9

VDD

L1

VDDL

E1

VREF

E2

VDDQ

C9

VSS

A3

VSS

E3

VDDQ

A9

VDD

E9

RFU1

G1

RFU2

L3

C

KE

F2

CK

E8

CK

F8

C

AS

G7

R

AS

F7

WE

F3

CS

G8

VDDQ

C1

VDDQ

C3

VDDQ

C7

VSSQ

B2

VSSQ

B8

VSSQ

D2

VSSQ

D8

VDD

A1

VSS

J1

A11

K7

BA1

G3

A12

L2

A13

L8

VSS

K9

VSSDL

E7

VSSQ

A7

RFU3

L7

C

9

2 10

0

n

F

C

9

2 10

0

n

F

C95 100nFC95 100nF

C100

100nF

C100

100nF

C

9

0 10

0

n

F

C

9

0 10

0

n

F

C103 100nFC103 100nF

C

88 100nF

C

88 100nF

C

9

6 10

0

n

F

C

9

6 10

0

n

F

C102

100nF

C102

100nF

R47

DNP

R47

DNP

C89 100nFC89 100nF

C106 100nFC106 100nF

C99 100nFC99 100nF

C97 100nFC97 100nF

R44

0

R

R44

0

R

C91 100nFC91 100nF

C105 100nFC105 100nF

C98 10

0

nFC98 10

0

nF

C84

1

00nFC84

1

00nF

C

8

6

1

00nFC

8

6

1

00nF

C85 100nFC85 100nF