Datasheet

Table Of Contents

- Features

- Description

- Block Diagram

- SFR Mapping

- Pin Configurations

- Oscillators

- Enhanced Features

- Dual Data Pointer Register DPTR

- Expanded RAM (XRAM)

- Reset

- Power Monitor

- Timer 2

- Programmable Counter Array PCA

- Serial I/O Port

- Interrupt System

- Power Management

- Keyboard Interface

- 2-wire Interface (TWI)

- Serial Port Interface (SPI)

- Hardware Watchdog Timer

- ONCE(TM) Mode (ON Chip Emulation)

- Power-off Flag

- EEPROM Data Memory

- Reduced EMI Mode

- Flash Memory

- Electrical Characteristics

- Absolute Maximum Ratings

- DC Parameters

- AC Parameters

- Explanation of the AC Symbols

- External Program Memory Characteristics

- External Program Memory Read Cycle

- External Data Memory Characteristics

- External Data Memory Write Cycle

- External Data Memory Read Cycle

- Serial Port Timing - Shift Register Mode

- Shift Register Timing Waveforms

- External Clock Drive Waveforms

- AC Testing Input/Output Waveforms

- Float Waveforms

- Clock Waveforms

- Ordering Information

- Packaging Information

- Table of Contents

93

AT89C51ID2

4289C–8051–11/05

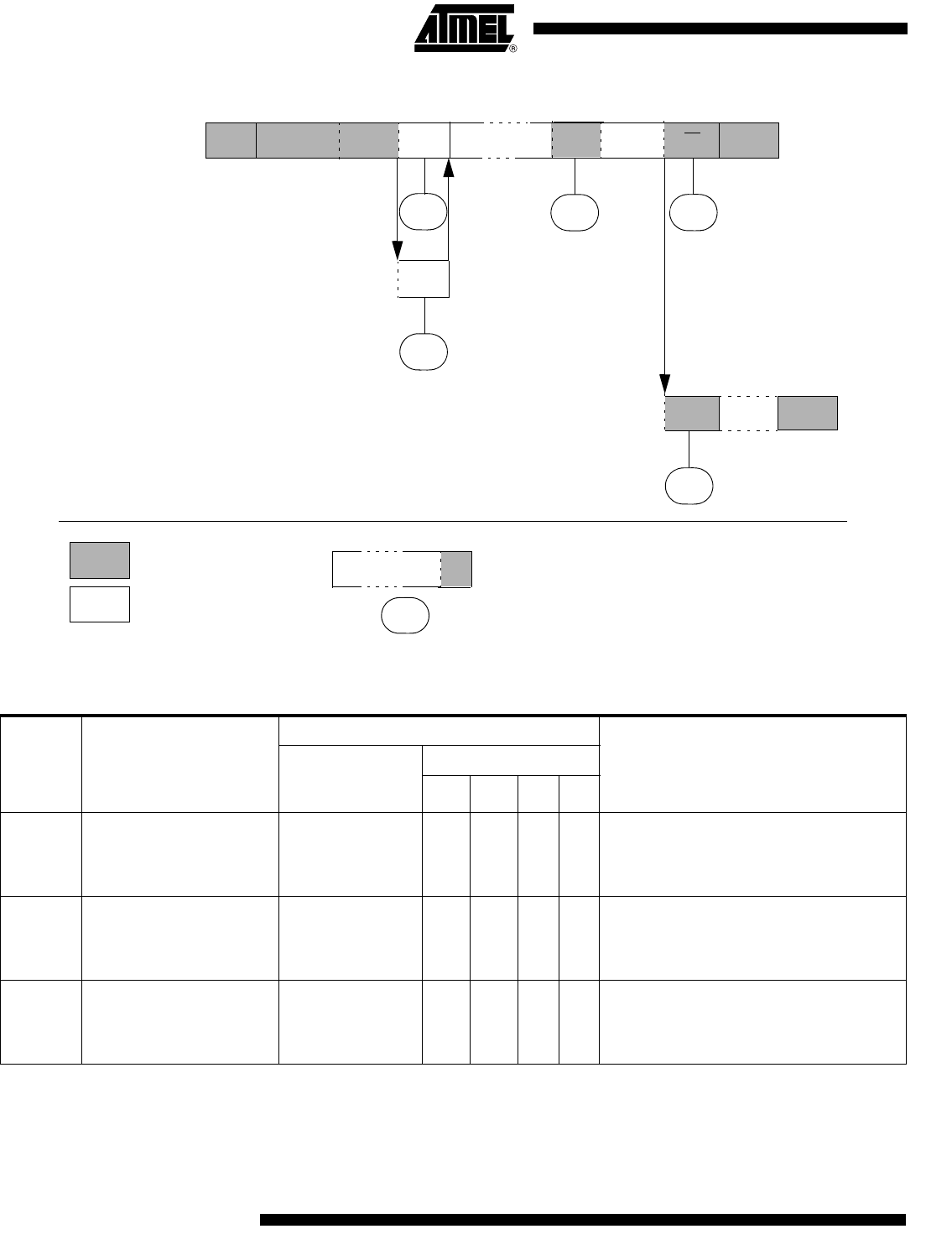

Figure 35. Format and State in the Slave Transmitter Mode

SSLAR

A

Data

A

Data

P or S

A

A8h

B8h

C0h

P or S

A

C8h

All 1’s

A

B0h

Data A

n

From master to slave

From slave to master

Any number of data bytes and their associated

acknowledge bits

This number (contained in SSCS) corresponds

to a defined state of the 2-wire bus

Reception of the

own slave address

and one or more

data bytes

Arbitration lost as master

and addressed as slave

Last data byte transmitted.

Switched to not addressed

slave (AA=0)

Table 69. Status in Slave Transmitter Mode

Status

Code

(SSCS)

Status of the 2-wire bus and

2-wire hardware

Application Software Response

Next Action Taken By 2-wire Software

To/from SSDAT To SSCON

STA STO SI AA

A8h

Own SLA+R has been

received; ACK has been

returned

Load data byte or

Load data byte

X

X

0

0

0

0

0

1

Last data byte will be transmitted and NOT ACK

will be received

Data byte will be transmitted and ACK will be

received

B0h

Arbitration lost in SLA+R/W as

master; own SLA+R has been

received; ACK has been

returned

Load data byte or

Load data byte

X

X

0

0

0

0

0

1

Last data byte will be transmitted and NOT ACK

will be received

Data byte will be transmitted and ACK will be

received

B8h

Data byte in SSDAT has been

transmitted; NOT ACK has

been received

Load data byte or

Load data byte

X

X

0

0

0

0

0

1

Last data byte will be transmitted and NOT ACK

will be received

Data byte will be transmitted and ACK will be

received