Datasheet

Table Of Contents

- Features

- Description

- Block Diagram

- SFR Mapping

- Pin Configurations

- Oscillators

- Enhanced Features

- Dual Data Pointer Register DPTR

- Expanded RAM (XRAM)

- Reset

- Power Monitor

- Timer 2

- Programmable Counter Array PCA

- Serial I/O Port

- Interrupt System

- Power Management

- Keyboard Interface

- 2-wire Interface (TWI)

- Serial Port Interface (SPI)

- Hardware Watchdog Timer

- ONCE(TM) Mode (ON Chip Emulation)

- Power-off Flag

- EEPROM Data Memory

- Reduced EMI Mode

- Flash Memory

- Electrical Characteristics

- Absolute Maximum Ratings

- DC Parameters

- AC Parameters

- Explanation of the AC Symbols

- External Program Memory Characteristics

- External Program Memory Read Cycle

- External Data Memory Characteristics

- External Data Memory Write Cycle

- External Data Memory Read Cycle

- Serial Port Timing - Shift Register Mode

- Shift Register Timing Waveforms

- External Clock Drive Waveforms

- AC Testing Input/Output Waveforms

- Float Waveforms

- Clock Waveforms

- Ordering Information

- Packaging Information

- Table of Contents

91

AT89C51ID2

4289C–8051–11/05

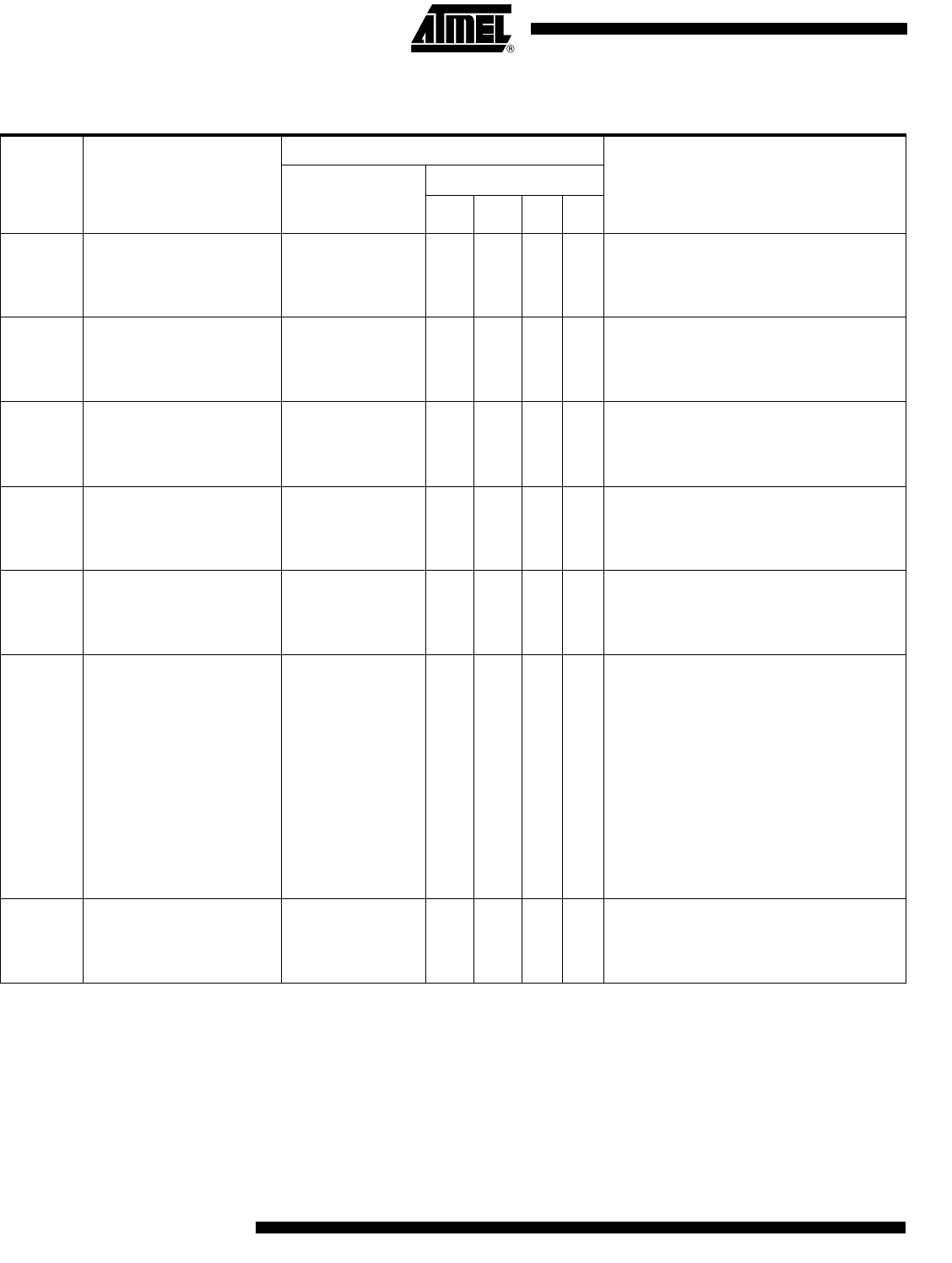

Table 68. Status in Slave Receiver Mode

Status

Code

(SSCS)

Status of the 2-wire bus and

2-wire hardware

Application Software Response

Next Action Taken By 2-wire Software

To/from SSDAT To SSCON

STA STO SI AA

60h

Own SLA+W has been

received; ACK has been

returned

No SSDAT action or

No SSDAT action

X

X

0

0

0

0

0

1

Data byte will be received and NOT ACK will be

returned

Data byte will be received and ACK will be

returned

68h

Arbitration lost in SLA+R/W as

master; own SLA+W has been

received; ACK has been

returned

No SSDAT action or

No SSDAT action

X

X

0

0

0

0

0

1

Data byte will be received and NOT ACK will be

returned

Data byte will be received and ACK will be

returned

70h

General call address has been

received; ACK has been

returned

No SSDAT action or

No SSDAT action

X

X

0

0

0

0

0

1

Data byte will be received and NOT ACK will be

returned

Data byte will be received and ACK will be

returned

78h

Arbitration lost in SLA+R/W as

master; general call address

has been received; ACK has

been returned

No SSDAT action or

No SSDAT action

X

X

0

0

0

0

0

1

Data byte will be received and NOT ACK will be

returned

Data byte will be received and ACK will be

returned

80h

Previously addressed with

own SLA+W; data has been

received; ACK has been

returned

No SSDAT action or

No SSDAT action

X

X

0

0

0

0

0

1

Data byte will be received and NOT ACK will be

returned

Data byte will be received and ACK will be

returned

88h

Previously addressed with

own SLA+W; data has been

received; NOT ACK has been

returned

Read data byte or

Read data byte or

Read data byte or

Read data byte

0

0

1

1

0

0

0

0

0

0

0

0

0

1

0

1

Switched to the not addressed slave mode; no

recognition of own SLA or GCA

Switched to the not addressed slave mode; own

SLA will be recognised; GCA will be recognised if

GC=logic 1

Switched to the not addressed slave mode; no

recognition of own SLA or GCA. A START

condition will be transmitted when the bus

becomes free

Switched to the not addressed slave mode; own

SLA will be recognised; GCA will be recognised if

GC=logic 1. A START condition will be

transmitted when the bus becomes free

90h

Previously addressed with

general call; data has been

received; ACK has been

returned

Read data byte or

Read data byte

X

X

0

0

0

0

0

1

Data byte will be received and NOT ACK will be

returned

Data byte will be received and ACK will be

returned