Datasheet

Table Of Contents

- Features

- Description

- Block Diagram

- SFR Mapping

- Pin Configurations

- Oscillators

- Enhanced Features

- Dual Data Pointer Register DPTR

- Expanded RAM (XRAM)

- Reset

- Power Monitor

- Timer 2

- Programmable Counter Array PCA

- Serial I/O Port

- Interrupt System

- Power Management

- Keyboard Interface

- 2-wire Interface (TWI)

- Serial Port Interface (SPI)

- Hardware Watchdog Timer

- ONCE(TM) Mode (ON Chip Emulation)

- Power-off Flag

- EEPROM Data Memory

- Reduced EMI Mode

- Flash Memory

- Electrical Characteristics

- Absolute Maximum Ratings

- DC Parameters

- AC Parameters

- Explanation of the AC Symbols

- External Program Memory Characteristics

- External Program Memory Read Cycle

- External Data Memory Characteristics

- External Data Memory Write Cycle

- External Data Memory Read Cycle

- Serial Port Timing - Shift Register Mode

- Shift Register Timing Waveforms

- External Clock Drive Waveforms

- AC Testing Input/Output Waveforms

- Float Waveforms

- Clock Waveforms

- Ordering Information

- Packaging Information

- Table of Contents

89

AT89C51ID2

4289C–8051–11/05

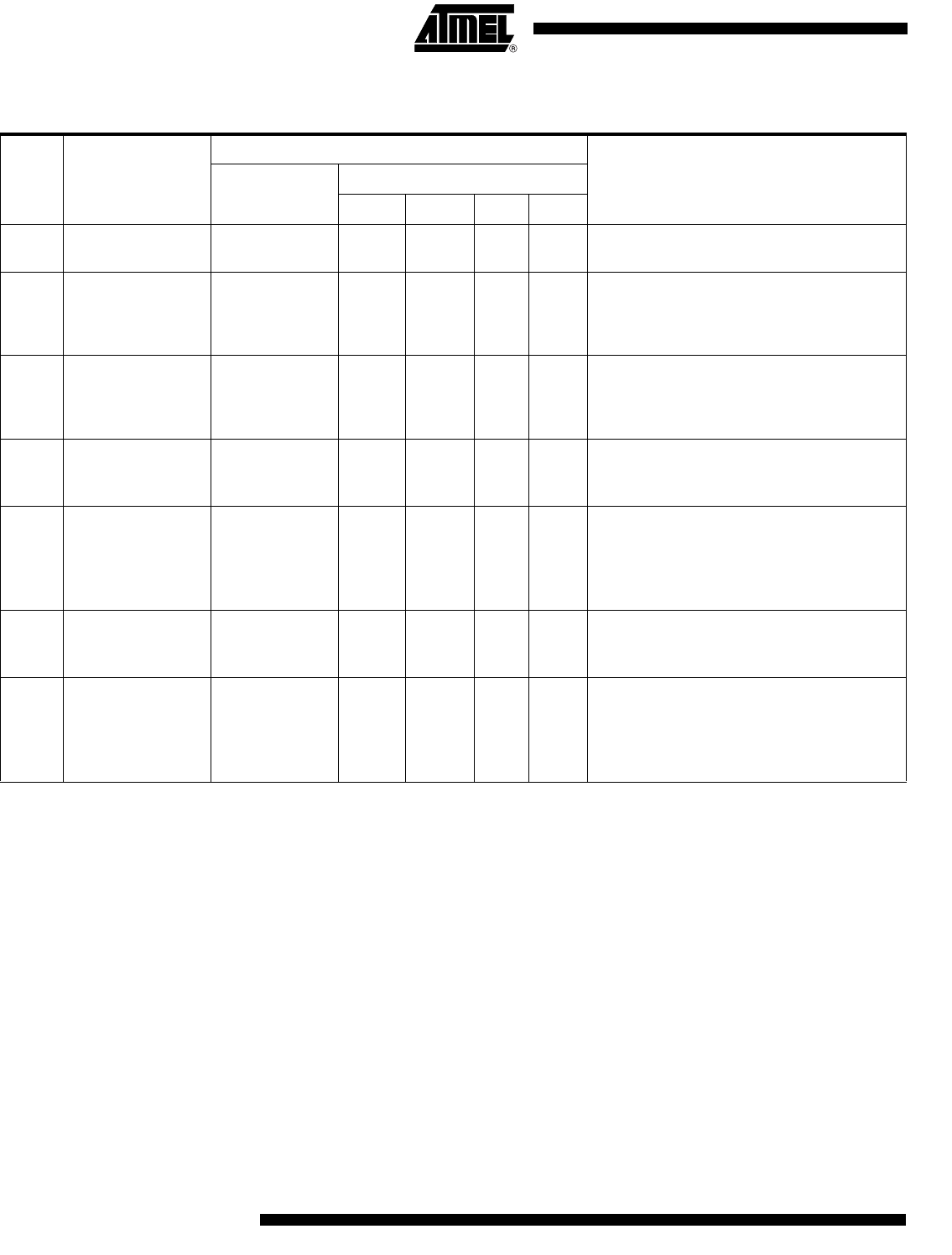

Table 67. Status in Master Receiver Mode

Status

Code

SSSTA

Status of the Two-

wire Bus and Two-

wire Hardware

Application software response

Next Action Taken by Two-wire HardwareTo/From SSDAT

To SSCON

SSSTA SSSTO SSI SSAA

08h

A START condition has

been transmitted

Write SLA+R X 0 0 X SLA+R will be transmitted.

10h

A repeated START

condition has been

transmitted

Write SLA+R

Write SLA+W

X

X

0

0

0

0

X

X

SLA+R will be transmitted.

SLA+W will be transmitted.

Logic will switch to master transmitter mode.

38h

Arbitration lost in

SLA+R or NOT ACK

bit

No SSDAT action

No SSDAT action

0

1

0

0

0

0

X

X

Two-wire bus will be released and not addressed

slave mode will be entered.

A START condition will be transmitted when the bus

becomes free.

40h

SLA+R has been

transmitted; ACK has

been received

No SSDAT action

No SSDAT action

0

0

0

0

0

0

0

1

Data byte will be received and NOT ACK will be

returned.

Data byte will be received and ACK will be returned.

48h

SLA+R has been

transmitted; NOT ACK

has been received

No SSDAT action

No SSDAT action

No SSDAT action

1

0

1

0

1

1

0

0

0

X

X

X

Repeated START will be transmitted.

STOP condition will be transmitted and SSSTO flag

will be reset.

STOP condition followed by a START condition will

be transmitted and SSSTO flag will be reset.

50h

Data byte has been

received; ACK has

been returned

Read data byte

Read data byte

0

0

0

0

0

0

0

1

Data byte will be received and NOT ACK will be

returned.

Data byte will be received and ACK will be returned.

58h

Data byte has been

received; NOT ACK

has been returned

Read data byte

Read data byte

Read data byte

1

0

1

0

1

1

0

0

0

X

X

X

Repeated START will be transmitted.

STOP condition will be transmitted and SSSTO flag

will be reset.

STOP condition followed by a START condition will

be transmitted and SSSTO flag will be reset.