Datasheet

Table Of Contents

- Features

- Description

- Block Diagram

- SFR Mapping

- Pin Configurations

- Oscillators

- Enhanced Features

- Dual Data Pointer Register DPTR

- Expanded RAM (XRAM)

- Reset

- Power Monitor

- Timer 2

- Programmable Counter Array PCA

- Serial I/O Port

- Interrupt System

- Power Management

- Keyboard Interface

- 2-wire Interface (TWI)

- Serial Port Interface (SPI)

- Hardware Watchdog Timer

- ONCE(TM) Mode (ON Chip Emulation)

- Power-off Flag

- EEPROM Data Memory

- Reduced EMI Mode

- Flash Memory

- Electrical Characteristics

- Absolute Maximum Ratings

- DC Parameters

- AC Parameters

- Explanation of the AC Symbols

- External Program Memory Characteristics

- External Program Memory Read Cycle

- External Data Memory Characteristics

- External Data Memory Write Cycle

- External Data Memory Read Cycle

- Serial Port Timing - Shift Register Mode

- Shift Register Timing Waveforms

- External Clock Drive Waveforms

- AC Testing Input/Output Waveforms

- Float Waveforms

- Clock Waveforms

- Ordering Information

- Packaging Information

- Table of Contents

3

AT89C51ID2

4289C–8051–11/05

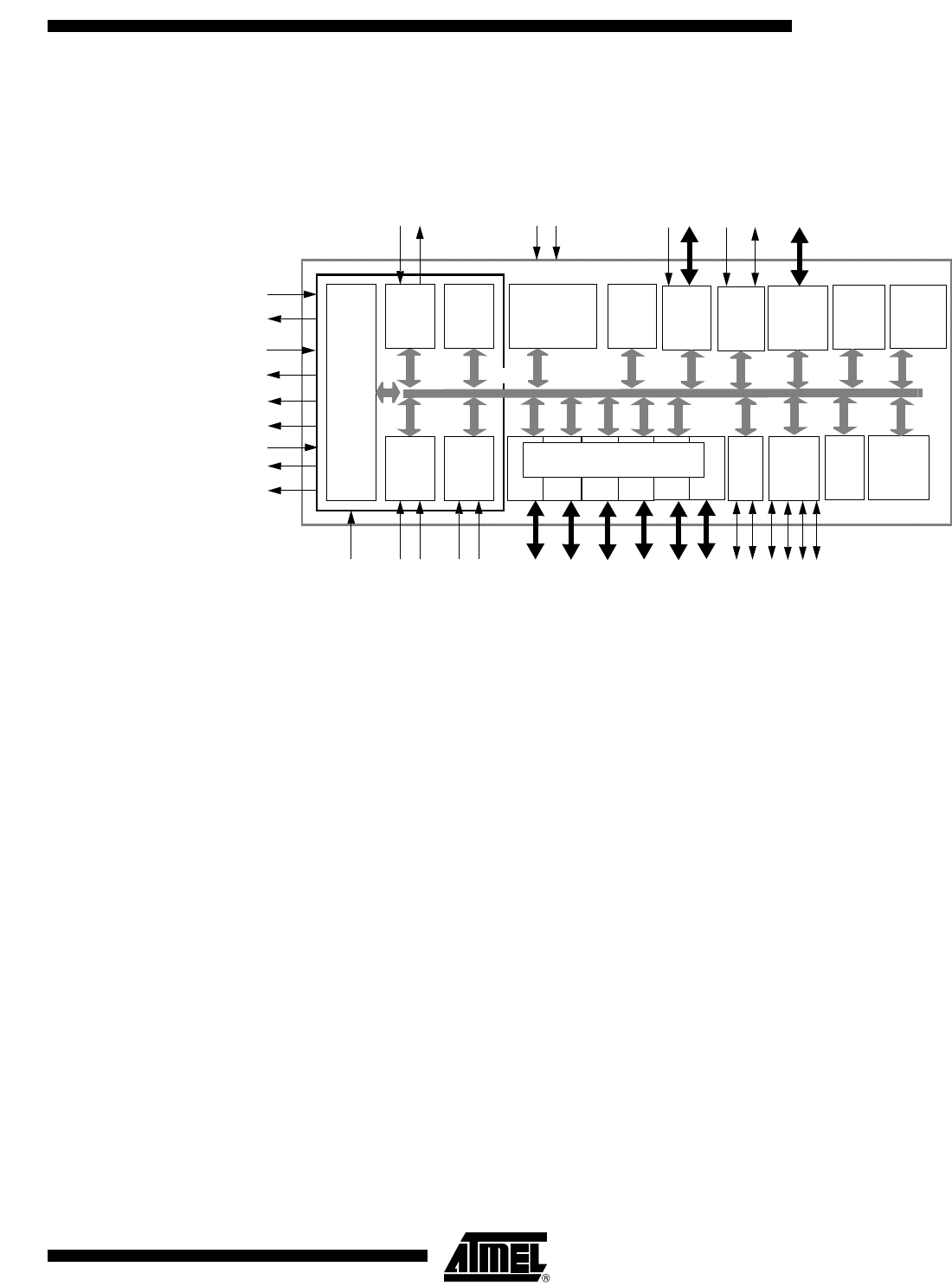

Block Diagram

Figure 1. Block Diagram

Timer 0

INT

RAM

256x8

T0

T1

RxD

TxD

WR

RD

EA

PSEN

ALE/

XTALA2

XTALA1

EUART

CPU

Timer 1

INT1

Ctrl

INT0

(2)

(2)

C51

CORE

(2) (2) (2) (2)

Port 0

P0

Port 1

Port 2

Port 3

P1

P2

P3

XRAM

1792 x 8

IB-bus

PCA

RESET

PROG

Watch

Dog

PCA

ECI

Vss

VCC

(2)(2)

(1)

(1): Alternate function of Port 1

(2): Alternate function of Port 3

(1)

Timer2

T2EX

T2

(1) (1)

Flash

64Kx8

Keyboard

(1)

Keyboard

SDA

SCL

MISO

MOSI

SCK

SS

(3): Alternate function of Port I2

(3)

(3)

Port4

P4

(1)

(1)

(1)

(1)

BOOT

2K x8

ROM

Regulator

POR / PFD

Port 5

P5

Parallel I/O Ports &

External Bus

SPI

TWI

E² DATA

2K x 8

POR

PFD

XTALB2

XTALB1(1)