Datasheet

Table Of Contents

- Features

- Description

- Block Diagram

- SFR Mapping

- Pin Configurations

- Oscillators

- Enhanced Features

- Dual Data Pointer Register DPTR

- Expanded RAM (XRAM)

- Reset

- Power Monitor

- Timer 2

- Programmable Counter Array PCA

- Serial I/O Port

- Interrupt System

- Power Management

- Keyboard Interface

- 2-wire Interface (TWI)

- Serial Port Interface (SPI)

- Hardware Watchdog Timer

- ONCE(TM) Mode (ON Chip Emulation)

- Power-off Flag

- EEPROM Data Memory

- Reduced EMI Mode

- Flash Memory

- Electrical Characteristics

- Absolute Maximum Ratings

- DC Parameters

- AC Parameters

- Explanation of the AC Symbols

- External Program Memory Characteristics

- External Program Memory Read Cycle

- External Data Memory Characteristics

- External Data Memory Write Cycle

- External Data Memory Read Cycle

- Serial Port Timing - Shift Register Mode

- Shift Register Timing Waveforms

- External Clock Drive Waveforms

- AC Testing Input/Output Waveforms

- Float Waveforms

- Clock Waveforms

- Ordering Information

- Packaging Information

- Table of Contents

26

AT89C51ID2

4289C–8051–11/05

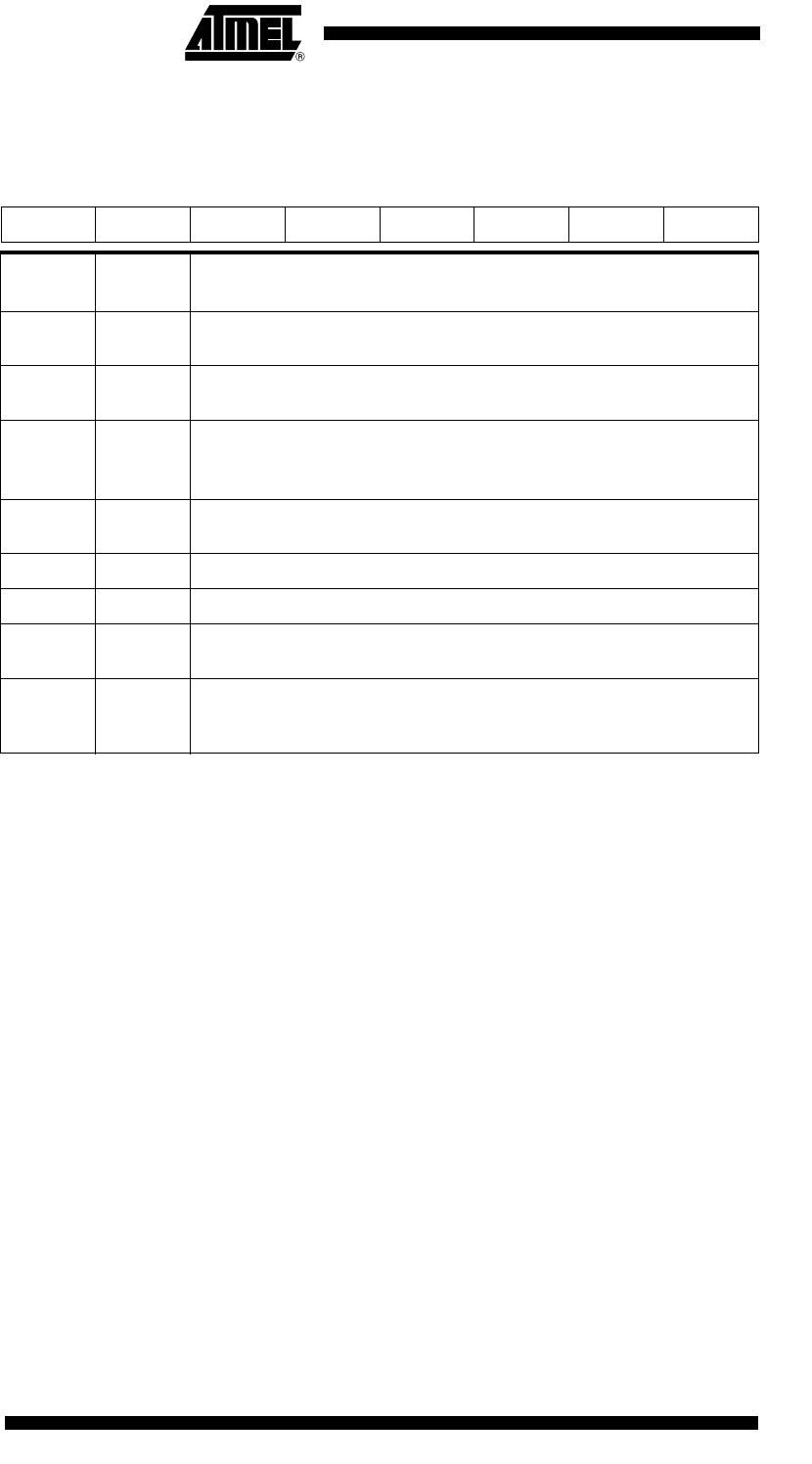

Table 23. AUXR1 register

AUXR1- Auxiliary Register 1(0A2h)

Reset Value: XXXX XX0X0b

Not bit addressable

Note: *Bit 2 stuck at 0; this allows to use INC AUXR1 to toggle DPS without changing GF3.

ASSEMBLY LANGUAGE

; Block move using dual data pointers

; Modifies DPTR0, DPTR1, A and PSW

; note: DPS exits opposite of entry state

; unless an extra INC AUXR1 is added

;

00A2 AUXR1 EQU 0A2H

;

0000 909000MOV DPTR,#SOURCE ; address of SOURCE

0003 05A2 INC AUXR1 ; switch data pointers

0005 90A000 MOV DPTR,#DEST ; address of DEST

0008 LOOP:

0008 05A2 INC AUXR1 ; switch data pointers

000A E0 MOVX A,@DPTR ; get a byte from SOURCE

000B A3 INC DPTR ; increment SOURCE address

000C 05A2 INC AUXR1 ; switch data pointers

000E F0 MOVX @DPTR,A ; write the byte to DEST

000F A3 INC DPTR ; increment DEST address

0010 70F6JNZ LOOP ; check for 0 terminator

0012 05A2 INC AUXR1 ; (optional) restore DPS

76543210

- - ENBOOT - GF3 0 - DPS

Bit

Number

Bit

Mnemonic Description

7-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

6-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

5ENBOOT

Enable Boot Flash

Cleared to disable boot ROM.

Set to map the boot ROM between F800h - 0FFFFh.

4-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

3GF3This bit is a general purpose user flag. *

20Always cleared.

1-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

0DPS

Data Pointer Selection

Cleared to select DPTR0.

Set to select DPTR1.