Datasheet

Table Of Contents

- Features

- Description

- Block Diagram

- SFR Mapping

- Pin Configurations

- Oscillators

- Enhanced Features

- Dual Data Pointer Register DPTR

- Expanded RAM (XRAM)

- Reset

- Power Monitor

- Timer 2

- Programmable Counter Array PCA

- Serial I/O Port

- Interrupt System

- Power Management

- Keyboard Interface

- 2-wire Interface (TWI)

- Serial Port Interface (SPI)

- Hardware Watchdog Timer

- ONCE(TM) Mode (ON Chip Emulation)

- Power-off Flag

- EEPROM Data Memory

- Reduced EMI Mode

- Flash Memory

- Electrical Characteristics

- Absolute Maximum Ratings

- DC Parameters

- AC Parameters

- Explanation of the AC Symbols

- External Program Memory Characteristics

- External Program Memory Read Cycle

- External Data Memory Characteristics

- External Data Memory Write Cycle

- External Data Memory Read Cycle

- Serial Port Timing - Shift Register Mode

- Shift Register Timing Waveforms

- External Clock Drive Waveforms

- AC Testing Input/Output Waveforms

- Float Waveforms

- Clock Waveforms

- Ordering Information

- Packaging Information

- Table of Contents

20

AT89C51ID2

4289C–8051–11/05

–F

CLK CPU

and F

CLK PERIPH

, for CKRL≠0xFF

In X2 Mode:

In X1 Mode:

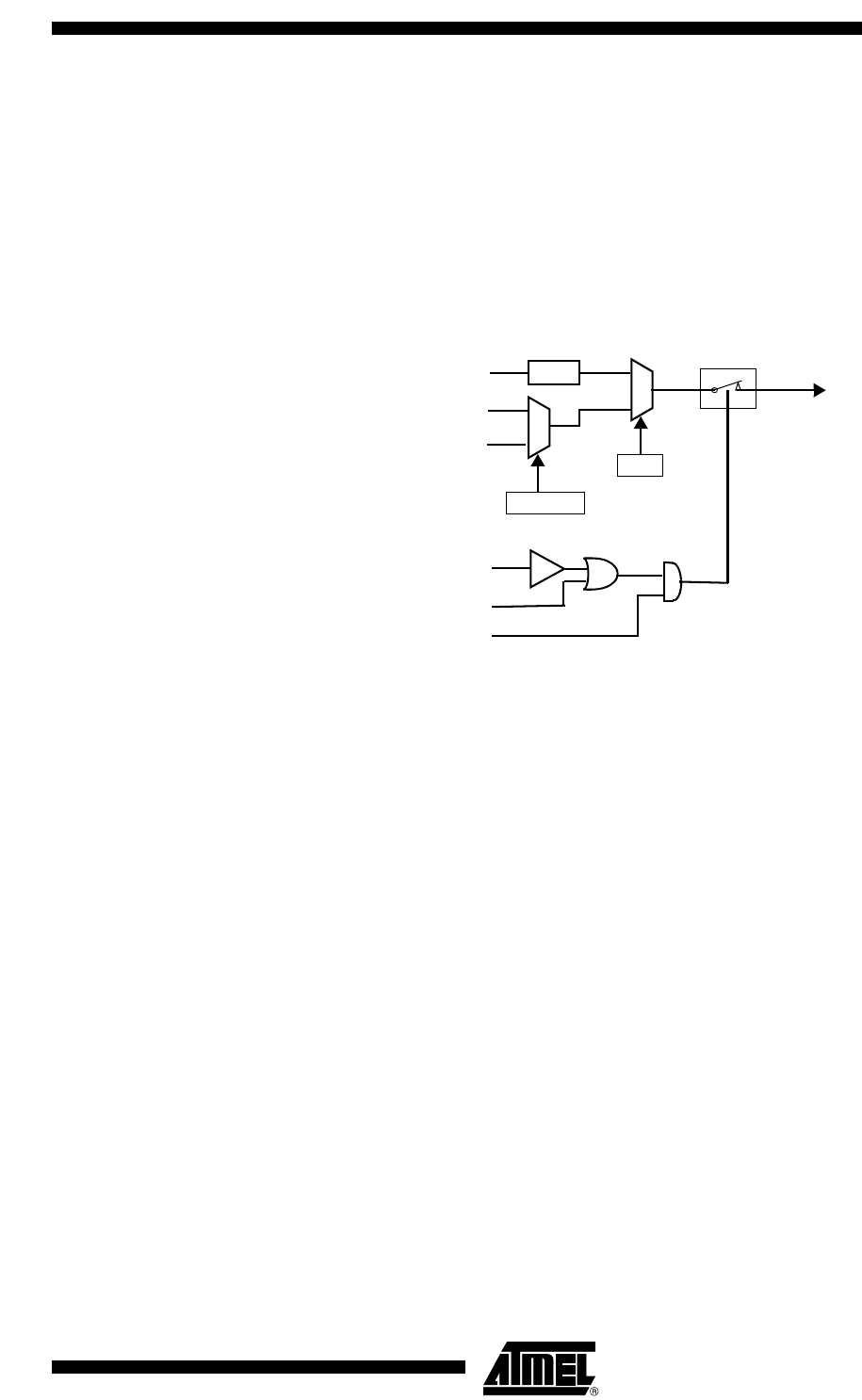

Timer 0: Clock Inputs Figure 1. Timer 0: Clock Inputs

Note: The SCLKT0 bit in OSCCON register allows to select Timer 0 Subsidiary clock.

SCLKT0 = 0: Timer 0 uses the standard T0 pin as clock input (Standard mode)

SCLKT0 = 1: Timer 0 uses the special Sub Clock as clock input, this feature can be use

as periodic interrupt for time clock.

F

CPU

F=

CLKPERIPH

F

OSCA

2255CKRL–()×

----------------------------------------------

=

F

CPU

F=

CLKPERIPH

F

OSCA

4255CKRL–()×

----------------------------------------------

=

SCLKT0

1

0

FCLK PERIPH

:6

T0 pin

C/T

1

0

OSCCON

TMOD

Gate

INT0

TR0

Timer 0

Control

Sub Clock

(AT 8xC51Ix2 only)