Datasheet

Table Of Contents

- Features

- Description

- Block Diagram

- SFR Mapping

- Pin Configurations

- Oscillators

- Enhanced Features

- Dual Data Pointer Register DPTR

- Expanded RAM (XRAM)

- Reset

- Power Monitor

- Timer 2

- Programmable Counter Array PCA

- Serial I/O Port

- Interrupt System

- Power Management

- Keyboard Interface

- 2-wire Interface (TWI)

- Serial Port Interface (SPI)

- Hardware Watchdog Timer

- ONCE(TM) Mode (ON Chip Emulation)

- Power-off Flag

- EEPROM Data Memory

- Reduced EMI Mode

- Flash Memory

- Electrical Characteristics

- Absolute Maximum Ratings

- DC Parameters

- AC Parameters

- Explanation of the AC Symbols

- External Program Memory Characteristics

- External Program Memory Read Cycle

- External Data Memory Characteristics

- External Data Memory Write Cycle

- External Data Memory Read Cycle

- Serial Port Timing - Shift Register Mode

- Shift Register Timing Waveforms

- External Clock Drive Waveforms

- AC Testing Input/Output Waveforms

- Float Waveforms

- Clock Waveforms

- Ordering Information

- Packaging Information

- Table of Contents

18

AT89C51ID2

4289C–8051–11/05

Idle Modes • IDLE modes are achieved by using any instruction that writes into PCON.0 bit (IDL)

• IDLE modes A and B depend on previous software sequence, prior to writing into

PCON.0 bit:

• IDLE MODE A: OscA is running (OscAEn = 1) and selected (CKS = 1)

• IDLE MODE B: OscB is running (OscBEn = 1) and selected (CKS = 0)

• The unused oscillator OscA or OscB can be stopped by software by clearing

OscAEn or OscBEn respectively.

• IDLE mode can be canceled either by Reset, or by activation of any enabled

interruption

• In both cases, PCON.0 bit (IDL) is cleared by hardware

• Exit from IDLE modes will leave Oscillators control bits (OscEnA, OscEnB, CKS)

unchanged.

Power Down Modes • POWER DOWN modes are achieved by using any instruction that writes into

PCON.1 bit (PD)

• POWER DOWN modes A and B depend on previous software sequence, prior to

writing into PCON.1 bit:

• Both OscA and OscB will be stopped.

• POWER DOWN mode can be cancelled either by a hardware Reset, an external

interruption, or the keyboard interrupt.

• By Reset signal: The CPU will restart according to OSC bit in Hardware Security Bit

(HSB) register.

• By INT0 or INT1 interruption, if enabled: (standard behavioral), request on Pads

must be driven low enough to ensure correct restart of the oscillator which was

selected when entering in Power down.

• By keyboard Interrupt if enabled: a hardware clear of the PCON.1 flag ensure the

restart of the oscillator which was selected when entering in Power down.

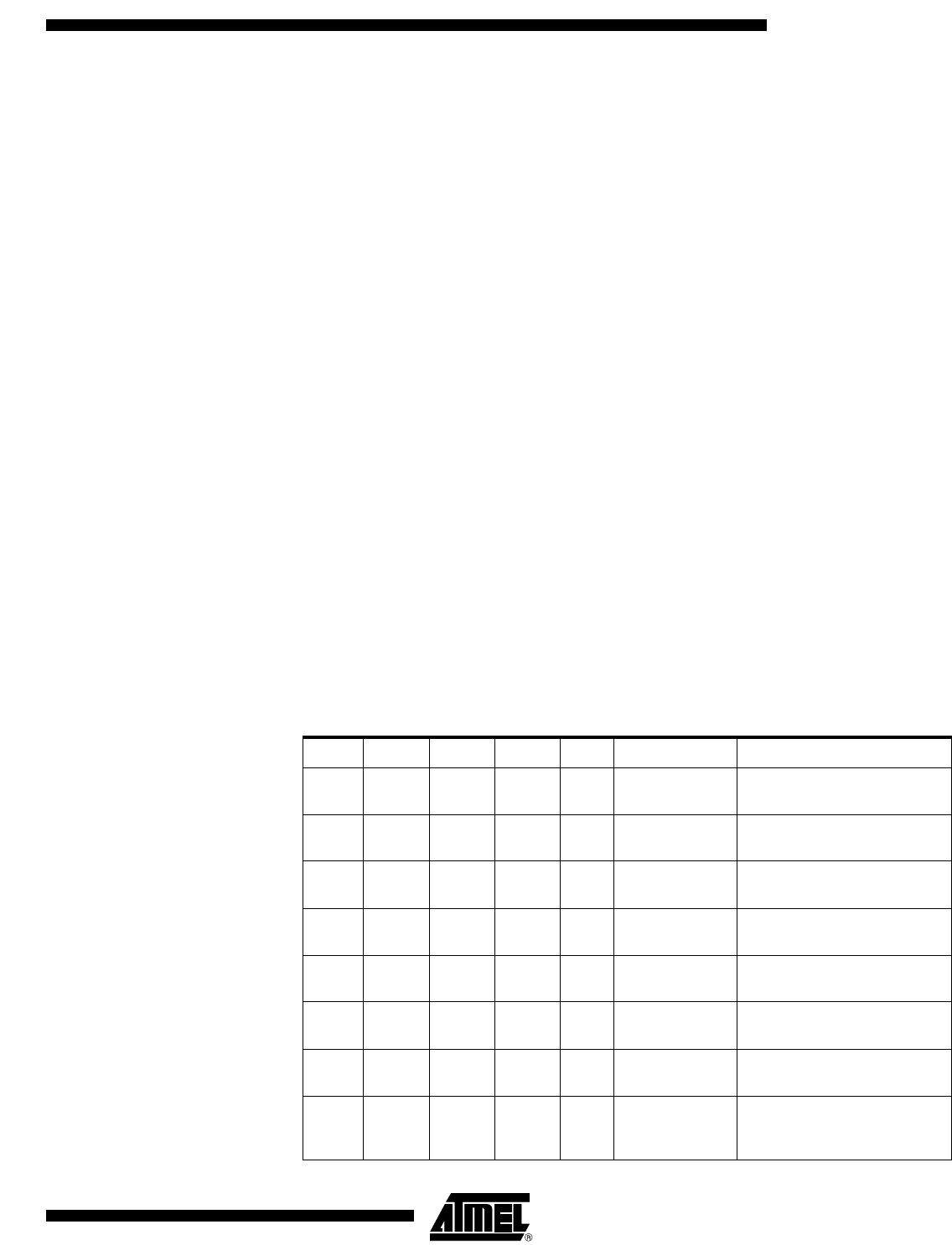

Table 20. Overview

PCON.1 PCON.0 OscBEn OscAEn CKS Selected Mode Comment

00 0 11

NORMAL MODE

A, OscB stopped

Default mode after power-up or

Warm Reset

00 1 11

NORMAL MODE

A, OscB running

Default mode after power-up or

Warm Reset + OscB running

00 1 00

NORMAL MODE

B, OscA stopped

OscB running and selected

00 1 10

NORMAL MODE

B, OscA running

OscB running and selected +

OscA running

XX 0 0XINVALID

OscA & OscB cannot be stopped

at the same time

XX X 01INVALID

OscA must not be stopped, as

used for CPU and peripherals

XX 0 X0INVALID

OscB must not be stopped as

used for CPU and peripherals

0 1 X 1 1 IDLE MODE A

The CPU is off, OscA supplies the

peripherals, OscB can be disabled

(OscBEn = 0)