Datasheet

Table Of Contents

- Features

- Description

- Block Diagram

- SFR Mapping

- Pin Configurations

- Oscillators

- Enhanced Features

- Dual Data Pointer Register DPTR

- Expanded RAM (XRAM)

- Reset

- Power Monitor

- Timer 2

- Programmable Counter Array PCA

- Serial I/O Port

- Interrupt System

- Power Management

- Keyboard Interface

- 2-wire Interface (TWI)

- Serial Port Interface (SPI)

- Hardware Watchdog Timer

- ONCE(TM) Mode (ON Chip Emulation)

- Power-off Flag

- EEPROM Data Memory

- Reduced EMI Mode

- Flash Memory

- Electrical Characteristics

- Absolute Maximum Ratings

- DC Parameters

- AC Parameters

- Explanation of the AC Symbols

- External Program Memory Characteristics

- External Program Memory Read Cycle

- External Data Memory Characteristics

- External Data Memory Write Cycle

- External Data Memory Read Cycle

- Serial Port Timing - Shift Register Mode

- Shift Register Timing Waveforms

- External Clock Drive Waveforms

- AC Testing Input/Output Waveforms

- Float Waveforms

- Clock Waveforms

- Ordering Information

- Packaging Information

- Table of Contents

149

AT89C51ID2

4289C–8051–11/05

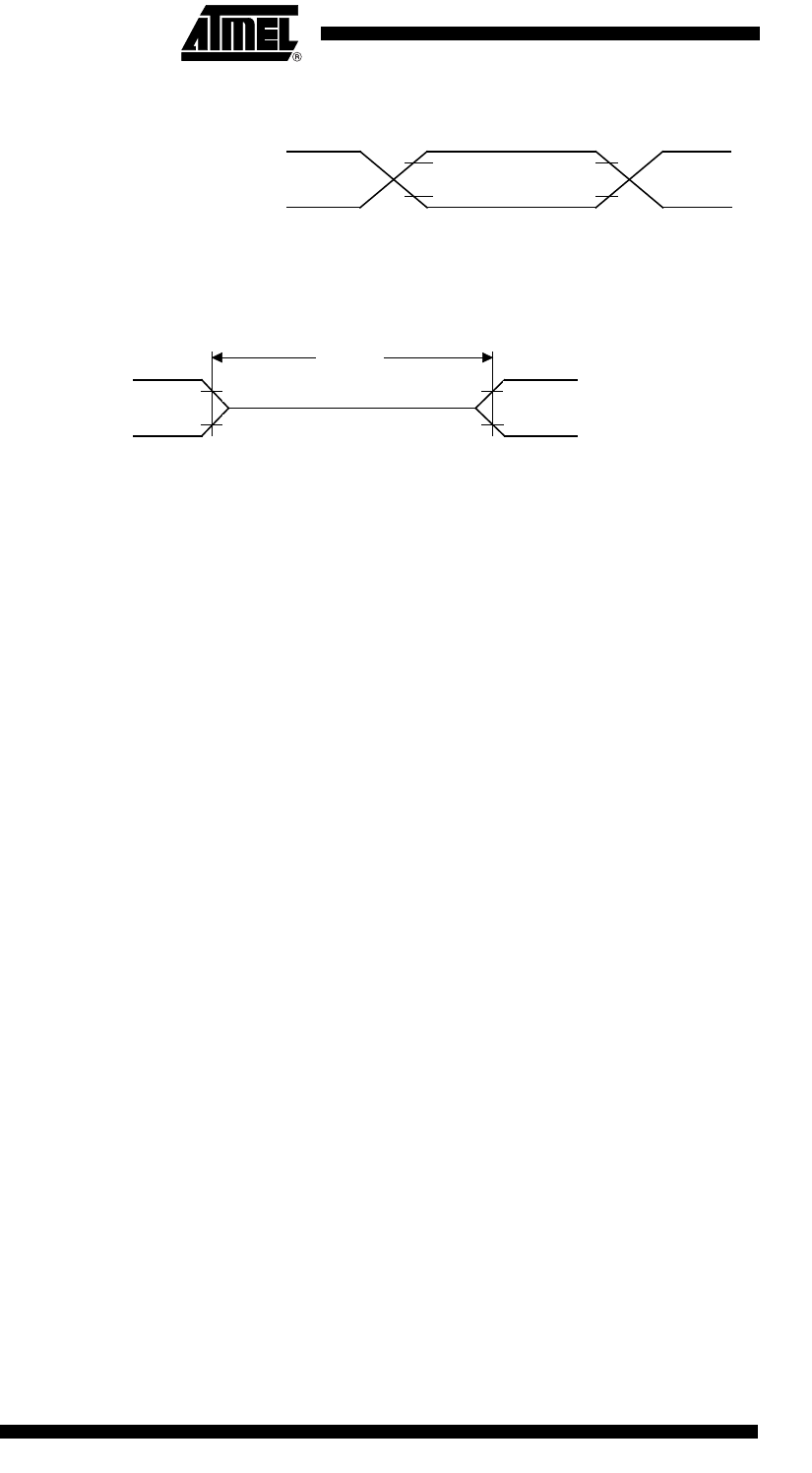

AC Testing Input/Output

Waveforms

AC inputs during testing are driven at V

CC

- 0.5 for a logic “1” and 0.45V for a logic “0”.

Timing measurement are made at V

IH

min for a logic “1” and V

IL

max for a logic “0”.

Float Waveforms

For timing purposes as port pin is no longer floating when a 100 mV change from load

voltage occurs and begins to float when a 100 mV change from the loaded V

OH

/V

OL

level

occurs. I

OL

/I

OH

≥ ± 20 mA.

Clock Waveforms Valid in normal clock mode. In X2 mode XTAL2 must be changed to XTAL2/2.

INPUT/OUTPUT

0.2 V

CC

+ 0.9

0.2 V

CC

- 0.1

V

CC

-0.5V

0.45V

FLOAT

V

OH

- 0.1V

V

OL

+ 0.1V

V

LOAD

V

LOAD

+ 0.1V

V

LOAD

- 0.1V