Datasheet

Table Of Contents

- Features

- Description

- Block Diagram

- SFR Mapping

- Pin Configurations

- Oscillators

- Enhanced Features

- Dual Data Pointer Register DPTR

- Expanded RAM (XRAM)

- Reset

- Power Monitor

- Timer 2

- Programmable Counter Array PCA

- Serial I/O Port

- Interrupt System

- Power Management

- Keyboard Interface

- 2-wire Interface (TWI)

- Serial Port Interface (SPI)

- Hardware Watchdog Timer

- ONCE(TM) Mode (ON Chip Emulation)

- Power-off Flag

- EEPROM Data Memory

- Reduced EMI Mode

- Flash Memory

- Electrical Characteristics

- Absolute Maximum Ratings

- DC Parameters

- AC Parameters

- Explanation of the AC Symbols

- External Program Memory Characteristics

- External Program Memory Read Cycle

- External Data Memory Characteristics

- External Data Memory Write Cycle

- External Data Memory Read Cycle

- Serial Port Timing - Shift Register Mode

- Shift Register Timing Waveforms

- External Clock Drive Waveforms

- AC Testing Input/Output Waveforms

- Float Waveforms

- Clock Waveforms

- Ordering Information

- Packaging Information

- Table of Contents

142

AT89C51ID2

4289C–8051–11/05

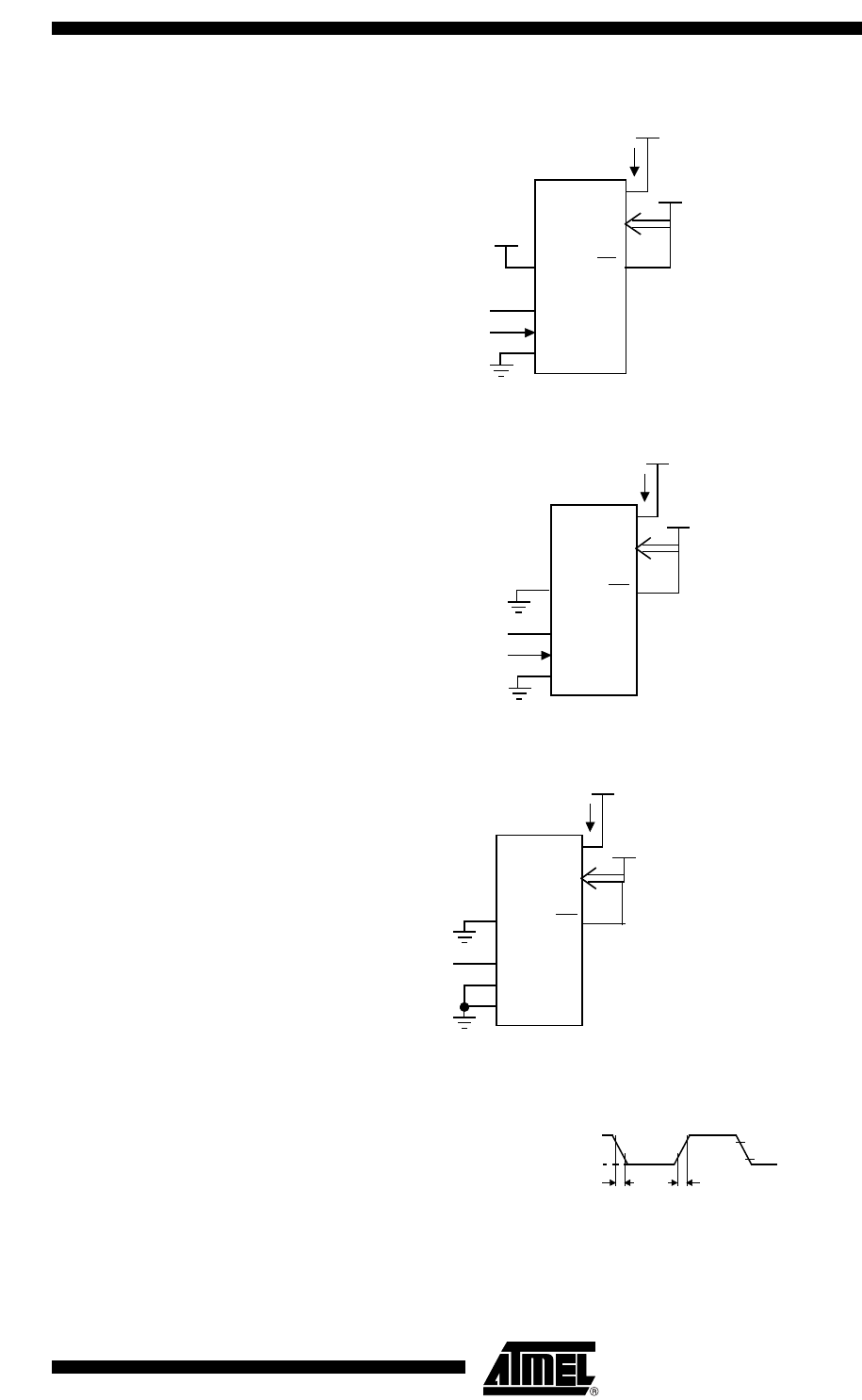

Figure 57. I

CC

Test Condition, Active Mode

Figure 58. I

CC

Test Condition, Idle Mode

Figure 59. I

CC

Test Condition, Power-down Mode

Figure 60. Clock Signal Waveform for I

CC

Tests in Active and Idle Modes

EA

V

CC

V

CC

I

CC

(NC)

CLOCK

SIGNAL

V

CC

All other pins are disconnected.

RST

XTAL2

XTAL1

V

SS

V

CC

P0

RST

EA

XTAL2

XTAL1

V

SS

V

CC

V

CC

I

CC

(NC)

P0

V

CC

All other pins are disconnected.

CLOCK

SIGNAL

RST

EA

XTAL2

XTAL1

V

SS

V

CC

V

CC

I

CC

(NC)

P0

V

CC

All other pins are disconnected.

V

CC

-0.5V

0.45V

0.7V

CC

0.2V

CC

-0.1

T

CLCH

T

CHCL

T

CLCH

= T

CHCL

= 5ns.