Specifications

Table Of Contents

- Table of Contents

- 1. Board Floorplan

- 2. PCB Errata

- 3. File Locations

- 4. Basic Operation

- 5. Jumpers and Connectors

- 6. Line-Side Connections

- 7. System Connectors

- 8. Microcontroller

- 9. Power-Supply Connectors

- 10. Connecting to a Computer

- 11. Installing and Running the Software

- 12. Address Map

- 13. Additional Information/Resources

- 14. Component List

- 15. Schematics

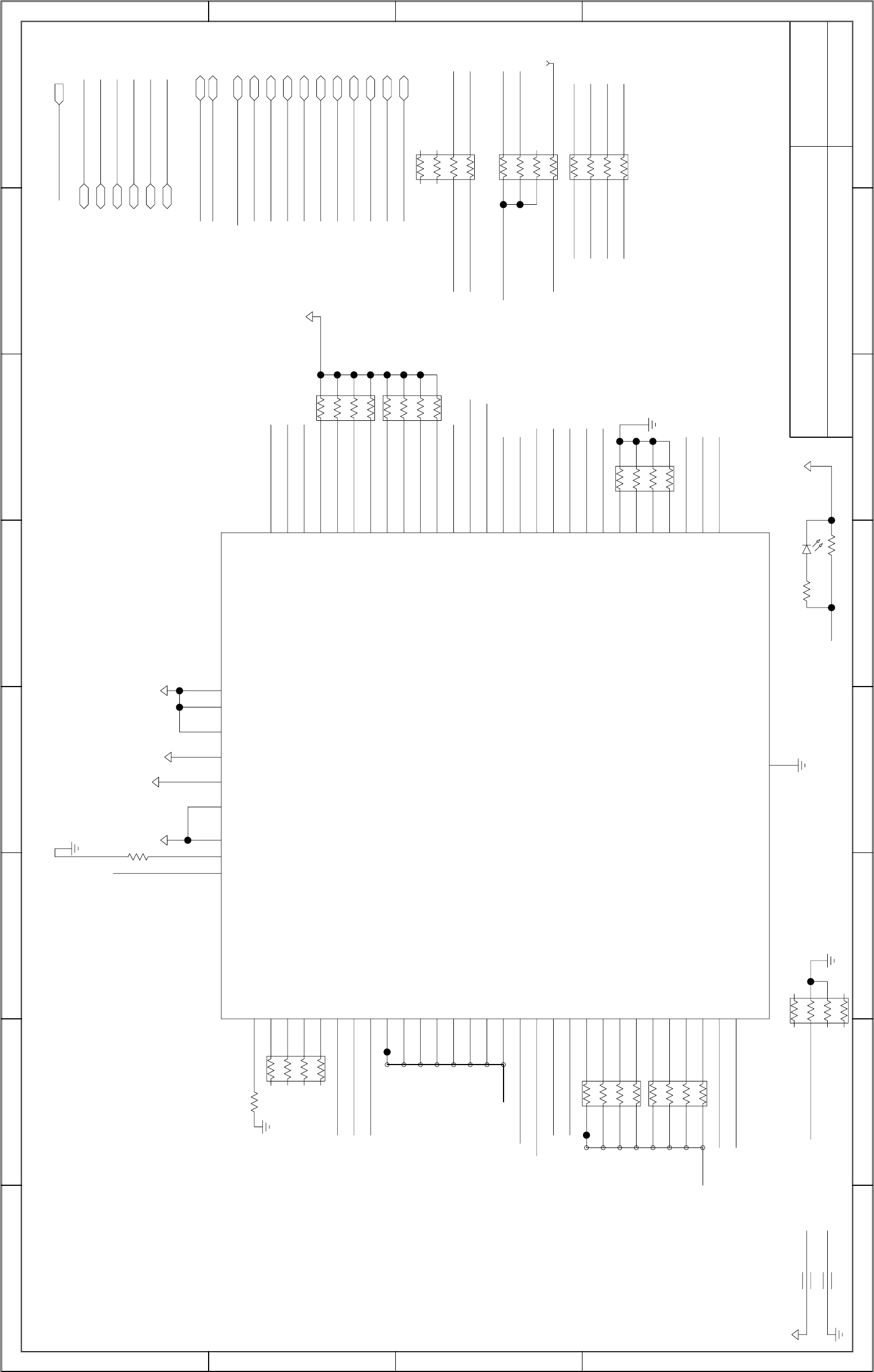

BEGIN PHY HIERARCHY BLOCK

CLOSE TO PHY

STIPLINE TO V2_5PHY

MAINTAIN 50OHM

PLACE MDI RESISTORS

PLACE 9.76K RES

CLOSE TO BG_REF

RXD[0:7] [PIN56:PIN45]

TXD[0:7] [PIN76:PIN65]

RXDV PIN44

OUTPUT

RXCLK PIN57

COL PIN39

CRS PIN40

RXER PIN41

TXCLK PIN60

CLKIN PIN86

GTXCLK PIN79

CLKTOMAC PIN85

CLKOUT PIN87

INPUT

MDC PIN81

TXERR PIN61

TXEN PIN62

2.0K

330

1K

GND

A0_DUPLEX

0603_2PCT_50

30

30

30

0603_2PCT_50

9.76K

30

1K

GREEN

30

30

2.0K

V3_3

RXD<7..0>

7

6

5

4

3

2

1

0

RX_CRS_BUF

TX_CLK_BUF

TX_EN

GMII_CLKFROM_MAC

TX_ER_

RX_ERR_BUF

RXDV_BUF

TXD<7..0>

COL_DET_BUF

RX_CLK_BUF

TX_ER_

7

6

5

4

3

2

1

0

BG_REF

RESET_B

PHYOSC25M

CLKOUT_BUF

ACTIVITYLED_SPEED0

NON_IEEE_STRAP

MDIO

MDC

MDIX_EN_STRAP

PHY_INT

MDIA_N

MDIB_P

MDIB_N

MDIA_P

MDIC_N

MDID_P

MDID_N

MDIC_P

CLKTOMAC_BUF

TX_CLK_BUF

CLKOUT_BUF

RX_CLK_BUF

COL_DET_BUF

RX_CRS_BUF

RX_ERR_BUF

RXDV_BUF

CLKTOMAC

RX_CRS

COL_DET

CLKTOMAC_TESTPNT

RX_CLK

TX_CLK

CLKOUT

RX_ERR

RXDV

RX_CRS

RXDV

TX_EN

RX_CLK

TX_CLK

RX_ERR

CLKTOMAC

TXD<7..0>

RXD<7..0>

COL_DET

GMII_CLKFROM_MAC

TX_ER_

CLKTOMAC_TESTPNT

PHYOSC25M

LAN_CLK

SPARE<4..1>

PHY_INT

MDIO

RESET_B

MDC

LINK100LED_DUPLEX

CLKTOMAC_BUF

MAN_MDIX_STRAP__TX_TCLK

LINK10LED_SPEED1

LINK1000LED_ANEN

6D4^

25A1

6D4^

25A1

6C4^25B7

6D4^

25B1

6C4^

25B1

6C4^

25A1

6C4^

25B1

6C4^25B7

6D4^25A8

6D4^

25B1

6C4^25B7

6C4^

25B725A7

25B1

6B4^25B3

6B4^

6B4^ 26C6 25C3

6B4^ 26C6 25C3

6B4^ 26C6 25D6

6B4^ 25C3

A0_DUPLEX

MULTI_EN_STRAP__TX_TRIGGER

MAC_CLK_EN_STRAP__TX_SYN_CLK

U04

98

100

7

102

86

87

85

39

40

79

3

10

9

8

88

6

81

109

108

115

114

121

120

127

126

80

89

94

1

13

14

17

18

95

33

57

44

41

56

55

52

51

50

47

46

45

24

31

28

27

32

60

62

61

76

75

72

71

68

67

66

65

34

RP05

4

3

2

1

5

6

7

8

RP07

4

3

2

1

5

6

7

8

RP06

4

3

2

1

5

6

7

8

RPB25

4

3

2

1

5

6

7

8

RP12

4

3

2

1

5

6

7

8

RB16

DS18

1

2

RPB20

4

3

2

1

5

6

7

8

RB06

RB07

RP02

4

3

2

1

5

6

7

8

RB11

TPB03

RPB30

4

3

2

1

5

6

7

8

RPB26

1

2

3

4

8

7

6

5

RPB24

1

2

3

4

8

7

6

5

10/03/2007

1/2(BLOCK)

25/26(TOTAL)

BLOCK NAME: _phy_dp83865bvh_dn. PARENT BLOCK: \_rc_top_dn_\

STEVE SCULLY

CR-25 : @\_RC_LIB\.\_RC_TOP_DN_\(SCH_1):PAGE5_I23@\_RC_LIB\.\_PHY_DP83865BVH_DN\(SCH_1):PAGE1

DS33M33DK01A0

ETHERNET. P.5-6,19,25-26

92

90

96

123

128

25A3

6D4^

25B1

25A2

25B2

6C4^

25C1

6C4^

25D1

6C4^

25A7

25C1

25A2

25A2

6C4^

25C1

25B2

25B2

6C4^ 25B7

25C1

25A4

6B4^26C625D2

6B4^

25D1

25B2

26B6

26C4

26D4

6B4^26C625D2

6B4^25D2

26C4

26C3

26C3

26C3

26C3

26B3

26B3

26B3

26C3

25B3

25C7

25B3

25C7

25C7

25A7

25A7

6C4^

25C1

6D4^

25C1

6D4^

25C1

6D4^

25C1

6C4^

25C1

6C4^

25C1

6D4^

25C1

26B6

25B2

26C4

26B6

26B6

26C4

PAGE:

DATE:

TITLE:

ENGINEER:

A A

B B

C C

D

D

1

1

2

2

3

3

4

45

56

6

7

7

8

8

V3_3

IO

IO

IO

V3_3

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IN

V2_5

V1_8

V2_5

V1_8

V3_3

IO

IO

IO

IO

DP83865_U

VSS<1..35>

MULTI_EN_STRAP/TX_TRIGGER

MAN_MDIX_STRAP/TX_TCLK

LINK10_LED/SPEED1_STRAP

LINK100_LED/DUPLEX_STRAP

LINK1000_LED/AN_EN_STRAP

MDIX_EN_STRAP

PHYADDR<1>_STRAP

DUPLEX_LED/PHYADDR<0>_STRAP

ACTIVITY_LED/SPEED0_STRAP

NON_IEEE_STRAP

PHYADDR<4>_STRAP

MAC_CLK_EN_STRAP/TX_SYN_CLK

PHYADDR<2>_STRAP

PHYADDR<3>_STRAP

CLK_TO_MAC

MDIB_N

MDIA_P

INTERRUPT*

MDIA_N

MDC

MDIO

CLK_IN

MDID_N

MDID_P

MDIC_N

MDIC_P

MDIB_P

CLK_OUT

RX_DV/RCK

RX_ER/RXDV_ER

RXD<7>

RXD<6>

RXD<5>

RXD<4>

RXD<3>/RX3

RXD<0>/RX0

RXD<2>/RX2

RXD<1>/RX1

RX_CLK

TX_ER

GTX_CLK/TCK

TX_EN/TXEN_ER

TXD<7>

TXD<6>

TXD<5>

TXD<4>

TXD<2>/TX2

TXD<3>/TX3

TXD<0>/TX0

TXD<1>/TX1

TX_CLK/RGMII_SEL0

CRS/RGMII_SEL1

COL

TMS

TCK

TDO

TDI

TRST*

RESET*

BG_REF

VDD_SEL_STRAP

1V8_AVDD3

1V8_AVDD2

1V8_AVDD1_<1..5>

2V5_AVDD<1..2>

IO_VDD<1..12>

CORE_VDD<1..8>