Specifications

Table Of Contents

- Table of Contents

- 1. Board Floorplan

- 2. PCB Errata

- 3. File Locations

- 4. Basic Operation

- 5. Jumpers and Connectors

- 6. Line-Side Connections

- 7. System Connectors

- 8. Microcontroller

- 9. Power-Supply Connectors

- 10. Connecting to a Computer

- 11. Installing and Running the Software

- 12. Address Map

- 13. Additional Information/Resources

- 14. Component List

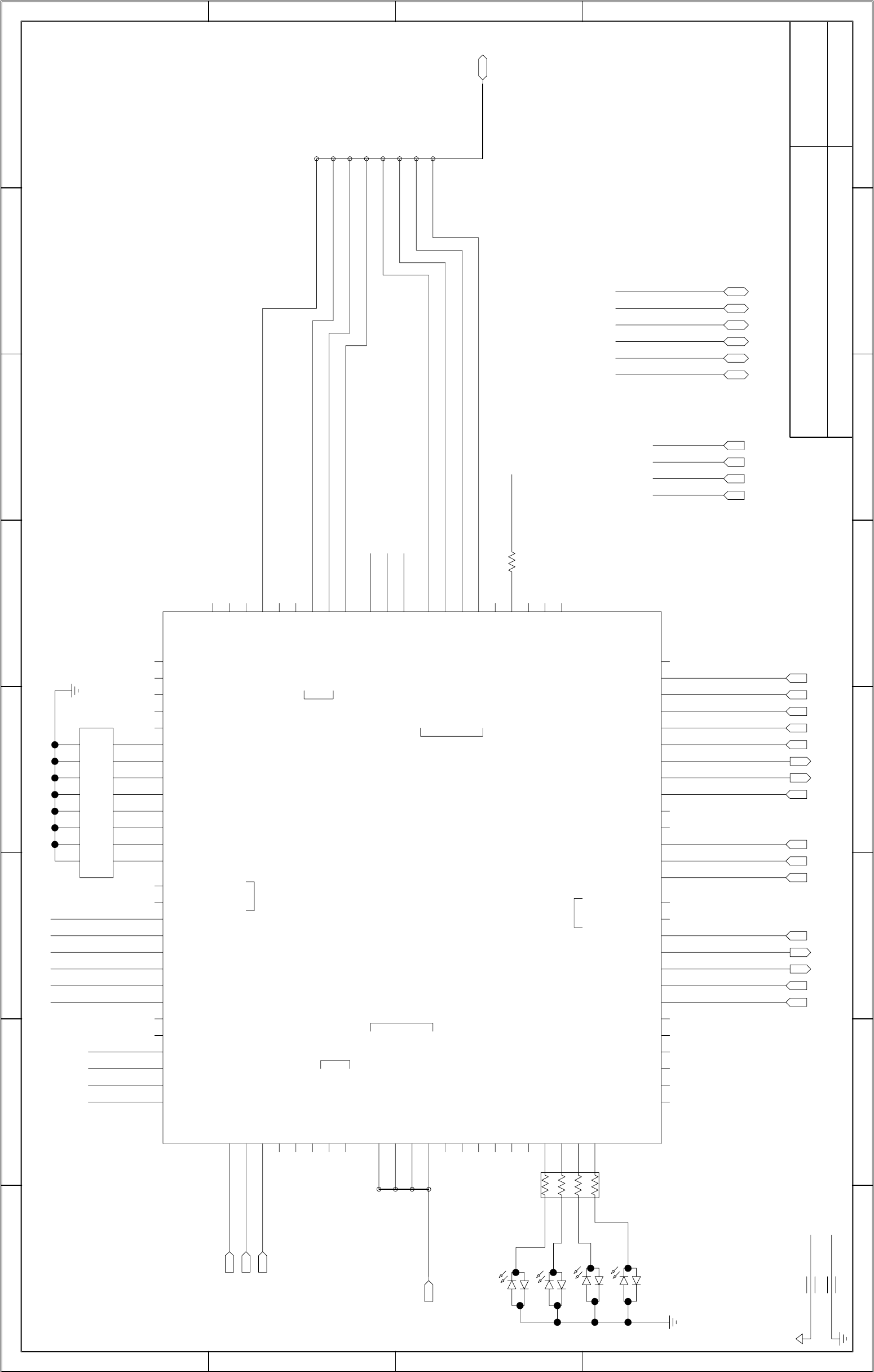

- 15. Schematics

MEM_SCK MUST BE AT PIN77 FOR TQFP144

SIGNALS FORSIGNALS FOR

HIERARCHY INTERFACE

BEGIN CPLD HIERARCHY BLOCK

MEM_SI

CP_DUT_CLKC

7

6

5

4

3

2

0

DAT<7..0>

V3_3

GND

RED_GREEN

330

CP_DUT_CLKA

CP_DUT_CLKB

0

1

2

3

WR

RD

CPLD_CS

CPLD_DTOHSOF

CPLD_ATOHCLK

CPLD_ATOHEN

CPLD_RDOHVLD

CPLD_OHCLK

CPLD_OH1

CPLD_TAOH

CPLD_TAOHSOF

CPLD_TAOHEN

CPLD_TAOHVLD

CPLD_RDOH

CPLD_ATOH

CPLD_ATOHSOF

CPLD_DTOH

CP_DUT_CLADCLK

CPLD_RDOHSOF

CP_DUT_CLKB

CP_DUT_CLKC

M33_GPIOA1

M33_GPIOB1

M33_GPIOA2

M33_GPIOB2

M33_GPIOB3

M33_GPIOA3

M33_GPIOB1

M33_GPIOA2

M33_GPIOB2

M33_GPIOA3

M33_GPIOB3

M33_GPIOA1

MEM_SCK

RED_GREEN

RED_GREEN

CP_DUT_CLADCLK

1

97_IO

CPLD_DTOHCLK

MEM_SO

MEM_CS

0.0

ADDR<3..0>

CP_DUT_CLKA

RED_GREEN

10B5^

RB04

U01

39

40

41

42

43

45

46

47

48

49

50

51

53

56

57

58

59

60

61

62

64

65

66

67

68

69

70

20

21

22

23

25

26

27

29

30

31

32

33

34

35

2

3

4

5

6

7

8

9

88

87

86

85

83

82

81

79

78

77

76

75

74

107

106

105

104

103

102

101

100

142

141

140

139

138

137

135

134

133

132

131

130

129

127

124

123

122

121

120

119

118

116

115

114

113

112

111

DS10

1

2

3

4

RP01

4

3

2

1

5

6

7

8

DS12

1

2

3

4

DS11

1

2

3

4

DS13

1

2

3

4

J02

1

2

3

4

5 6

7

8

9

10

11

12

13 14

15 16

23/26(TOTAL)

STEVE SCULLY

10/03/2007

1/2(BLOCK)

DS33M33DK01A0

BLOCK NAME: overheadcpld_dn_. PARENT BLOCK: \_rc_top_dn_\

OVERHEAD. P.2,10,23-24

CR-49 : @\_rc_lib\.\_rc_top_dn_\(sch_1):page12_i24@\_rc_lib\.\overheadcpld_dn_\(sch_1):Page1

11B5^

11B5^

11B5^

11B5^

11C5^

11C7^

11C5^

11C5^

11C5^

11C7^

11C7^

11C5^

11C5^

11B7^

11C7^

11C7^

11B7^

11B7^

11C7^

11C7^

49D711B7^

49D711B7^

49D711B7^

49D711B7^

24C8

10B7^23A3

10B7^23A3

10B7^23A3

24C8

24B8

10B7^23A3

PAGE:

DATE:

TITLE:

ENGINEER:

A A

B B

C C

D

D

1

1

2

2

3

3

4

45

56

6

7

7

8

8

BANK 3

LFEC_T144_U

BANK 0

I/O PORT

BANK 6

BANK 4BANK 5

BANK 1

BANK 2

INPUT

PLL

PLL

INPUT

PLL

INPUT

BANK 7

INPUT

PLL

INPUT

PLL

PLL

INPUT

PL9B/PCLKC7_0

PT16B/VREF1_0

PT17A/PCLKT0_0

PT15A

PT15B

PT16A/VREF2_0

PR14A/RLM0_PLLT_FB_A

PR12A/DOUT/CSO*

PT14B

PL14A

PL13B

PL13A

PT12B

PT12A

PB17A/PCLKT5_0

PB19A/VREF1_4

PB19B/CS*

PB20A/VREF2_4

PT14A/TDQS14

PT10A

PT10BPB10B

PB23A

PB22A/BDQS22

PB21A/D2/SPID5

PB18B/CS1*

PL11A/LLM0_PLLT_IN_A

PL11B/LLM0_PLLC_IN_A

PL12A/LLM0_PLLT_FB_A

PL12B/LLM0_PLLC_FB_A

PL14B

PL15B

PL15A/LDQS15

PL16B

PL18B/VREF2_6

PL18A/VREF1_6

PB18A/WRITE*

PB17B/PCLKC5_0

PB16A/VREF2_5

PB16B/VREF1_5

PB15B

PB15A

PB14B

PB14A/BDQS14

PB13B

PB11B

PB11A

PB10A

PL16A

PB20B/D0/SPID7

PB21B/D1/SPID6

PB22B/D3/SPID4

PB23B/D4/SPID3

PB25B/D6/SPID1

PB24B/D5/SPID2

PL2A/VREF2_7

PL2B/VREF1_7

PL7A

PL7B

PL8B

PL8A

PT25B

PT25A

PT23A

PT22B

PT22A/TDQS22

PT21B

PT20A

PT21A

PT20B

PT19B/VREF2_1

PT13B

PT13A

PT19A/VREF1_1

PT18B

PT18A

PR2B/VREF1_2

PR2A/VREF2_2

PR7B

PR7A

PR8A

PR8B

PR9A/PCLKT2_0

PR9B/PCLKC2_0

PR13A/RLM0_PLLT_IN_A

PR13B/RLM0_PLLC_IN_A

PR14B/RLM0_PLLC_FB_A

PR15A/RDQS15

PR16A

PR18A/VREF1_3

PR16B

PL9A/PCLKT7_0

PR15B

PT17B/PCLKC0_0

PR11A/D7/SPID0

PR11B/BUSY/SISPI

PR12B/DI/CSSPI*

IO

IO

IO

IO

IO

IO

IN

IN

IN

IN

CONN_16P

2

4

8

10

12

14

16

3

1

7

9

11

13

15

5 6

G

R

3

4 2

1

G

R

3

4 2

1

G

R

3

4 2

1

G

R

3

4 2

1

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT

IN

OUT

IN

IN

IN

IN

IO

V3_3