Specifications

Table Of Contents

- Table of Contents

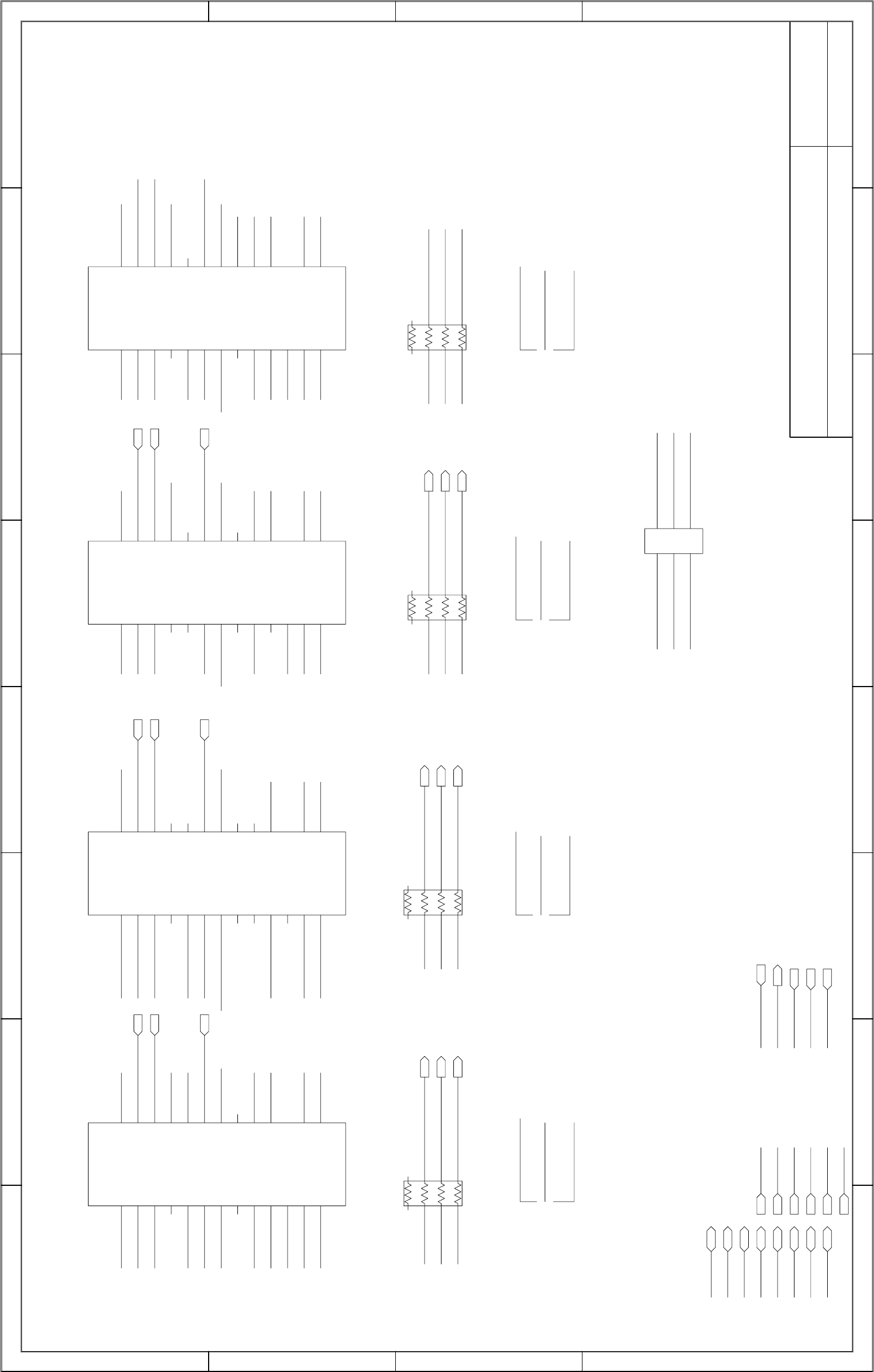

- 1. Board Floorplan

- 2. PCB Errata

- 3. File Locations

- 4. Basic Operation

- 5. Jumpers and Connectors

- 6. Line-Side Connections

- 7. System Connectors

- 8. Microcontroller

- 9. Power-Supply Connectors

- 10. Connecting to a Computer

- 11. Installing and Running the Software

- 12. Address Map

- 13. Additional Information/Resources

- 14. Component List

- 15. Schematics

DS3254 OR

PORT LOCATIONS

RLOS1 IS AT PIN A1

RLOS2 IS AT PIN M12

IT IS A SPARE PORT IN THIS DESIGN

DS3254 OR

DS3253 IS RECOMMENDED FOR DS33M33

PORT 4 OF DS3254 IS NOT USED WITH DS33M33

DS3254 OR

RLOS3 IS AT PIN A12

DS3254 OR

LIU_RPOS4

LIU_RCLK3

LIU_TCLK3

DATA6

DATA4

RCLK2

RXP2

RCLK1

RPOS1

RNEG4

LIU_TCLK4

ADDR5

ADDR5

RXN2

LIU_TPOS2

LIU_TNEG2

RTS2

ADDR4

RCLK2

TXP2

TXN2

TDM2

TTS2

PRBS2

LIU_TCLK2

RNEG2

RPOS2

RLOS2

TXP1

TXN1

RST

LIU_RNEG3

LIU_RPOS3

LIU_RCLK3

LIU_RCLK4

LIU_TCLK4

LIU_RCLK4

CS

INT

RCLK1

RNEG1

DATA0

LIU_TCLK1

DATA3

30

OSCSEL

RXN3

RCLK3

RPOS3

RNEG3

JMP_3

JMP_3

RCLK4

LIU_TCLK3

RLOS3

RPOS3

RNEG3

ALE

DATA2

RXP1

RXN1

PRBS3

ADDR2

DATA7

DATA6

DATA1

RTS1

RLOS1

RPOS1

TXP3

TDM1

LIU_TPOS1

LIU_RCLK1

LIU_TPOS4

LIU_TNEG4

TDM3

TTS1

RCLK3

TTS3

JMP_3

RPOS4

30

OSCSEL

30

LIU_RNEG1

LIU_RPOS1

RNEG1

PRBS1

RXP3

MOT

TXP4

TTS4

PRBS4

RPOS4

RLOS4

LIU_RCLK1

LIU_TPOS3

LIU_TNEG3

TXN3

RTS3

LIU_TNEG1

OSCSEL

RNEG4

LIU_RNEG4

LIU_RPOS4

LIU_RCLK4

TXN4

RCLK4

DATA4

TDM4

ADDR3

RTS4

ADDR1

RXP4

RXN4

DATA5

ADDR0

JMP_3

RD_DS

CS

WR_RW

OSCSEL

LIU_TCLK2

ADDR2

ADDR3

ADDR4

DATA0

DATA1

DATA2

DATA3

DATA7

DATA5

RD_DS

LIU_TCLK1

INT

LIU_RCLK2

LIU_TNEG4

LIU_TCLK4

LIU_TPOS4

LIU_RNEG4

WR_RW

ADDR1

ADDR0

30

LIU_RNEG2

RPOS2

RNEG2

LIU_RCLK2

LIU_RPOS2

9C3^21D3

9C3^21D7

9C3^21D7

9C3^21C8

9C3^21C8

9C3^21C7

9C3^21C2

9C3^21C3

U07

K6

H2

M2

M3

J2

H3

M1

J1

K3

L3

L2

L1

K1

L6

M5

K4

L7

K7

J3

K5

L4

M4

L5

M7

M6

U07

C7

E11

A11

A10

D11

E10

A12

D12

C10

B10

B11

B12

C12

B7

A8

C9

B6

C6

D10

C8

B9

A9

B8

A6

A7

U07

G10

L8

L12

K12

L9

K8

M12

M9

K10

K11

L11

M11

M10

G11

H12

J10

F11

F10

K9

H10

J11

J12

H11

F12

G12

U07

F3

B5

B1

C1

B4

C5

A1

A4

C3

C2

B2

A2

A3

F2

E1

D3

G2

G3

C4

E3

D2

D1

E2

G1

F1

JPB01

1

3

2

JP23

1

3

2

JP24

1

3

2

JP16

1

3

2

RPB35

4

3

2

1

5

6

7

8

RPB37

4

3

2

1

5

6

7

8

RPB31

4

3

2

1

5

6

7

8

RPB44

4

3

2

1

5

6

7

8

JB07

1

2

3

4

5 6

21/26(TOTAL)

2/3(BLOCK)

10/03/2007

BLOCK NAME: _ds3154_liublock_dn. PARENT BLOCK: \_rc_top_dn_\

DS33M33DK01A0

CR-47 : @\_rc_lib\.\_rc_top_dn_\(sch_1):page13_i204@\_rc_lib\.\_ds3154_liublock_dn\(sch_1):Page2

STEVE SCULLY

T3E3 LIU I/F. P.2,9,20-22

47B7

47B5

47B4

47B447B547B7

47C3

10C2^

47C3

10C2^

47D2

10C2^

47C2

10C2^

47D6

10C2^

47C8 10C2^

47C3 10C2^

47C4 10C2^

46B6

46C7 10B2^

46D8 47D8

10B2^

47C6

10C2^

21B2

21B3

21C3

21C6

22A5

21C8

21D8

21B221A4

9C2^ 21A8

22A5

22D8

9C2^

21A8

22B5

22B5

22A7

22C8

22C8

22B7

22D5

22D5

21B2

21C1

21A4

21B221A3

9B2^ 21A6 20D8

21B8

21B8

9C3^21A8

21B521B421B220A620A4

22C3

21C4

21D4

21D4

21C3

22B7

21B4

21B4

20D89C3^ 21A8

22C5

22C5

22B8

9C2^21A8

9C3^21A8

9C3^ 21A8

9C3^ 21A8

22D8

22B7

21B8

22D3

21B7

21A4

21A4

22A7

22C8 22C8

21D3

21B721B521B220A620A4

21D8

22C8

22C3

20D8

22B3

22C8

22B822B7

22D3

22C8

21B7

21B521B420A620A4

21D3 21A3

21A3

21B221A3

22B3

9C3^21A8

22A7

9C2^21A8

22C8

9C2^ 21A8

22A3

22A3

9C3^ 21A8

9C2^ 21A8

9C2^ 21A6

9C2^ 21A6

21B721B421B220A620A4

21C5

21C6

21B5

21D1

21C1

21B2

21D1

21B2

21D6

21D6

PAGE:

DATE:

TITLE:

ENGINEER:

A A

B B

C C

D

D

1

1

2

2

3

3

4

45

56

6

7

7

8

8

IN

OUT

IN

DS3154

PORT

TPOS

TNEG

RJA

RTS*

RMON

RLB

RCLK

STS

LLB

E3M

RXP

RXN

TXP

TXN

TDM*

TDSA

TDSB

TJA

TTS*

PRBS

TLBO

TCLK

RNEG

RPOS

RLOS*

IN

IN

IN

IO

IO

IO

IO

IO

IO

DS3154

PORT

TPOS

TNEG

RJA

RTS*

RMON

RLB

RCLK

STS

LLB

E3M

RXP

RXN

TXP

TXN

TDM*

TDSA

TDSB

TJA

TTS*

PRBS

TLBO

TCLK

RNEG

RPOS

RLOS*

IO

IN

IN

IN

IN

IN

IO

2

65

4

3

1

CONN_6P_U

IN

IN

DS3154

PORT

TPOS

TNEG

RJA

RTS*

RMON

RLB

RCLK

STS

LLB

E3M

RXP

RXN

TXP

TXN

TDM*

TDSA

TDSB

TJA

TTS*

PRBS

TLBO

TCLK

RNEG

RPOS

RLOS*

IN IN

IN

IN IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

DS3154

PORT

TPOS

TNEG

RJA

RTS*

RMON

RLB

RCLK

STS

LLB

E3M

RXP

RXN

TXP

TXN

TDM*

TDSA

TDSB

TJA

TTS*

PRBS

TLBO

TCLK

RNEG

RPOS

RLOS*