Specifications

Table Of Contents

- Table of Contents

- 1. Board Floorplan

- 2. PCB Errata

- 3. File Locations

- 4. Basic Operation

- 5. Jumpers and Connectors

- 6. Line-Side Connections

- 7. System Connectors

- 8. Microcontroller

- 9. Power-Supply Connectors

- 10. Connecting to a Computer

- 11. Installing and Running the Software

- 12. Address Map

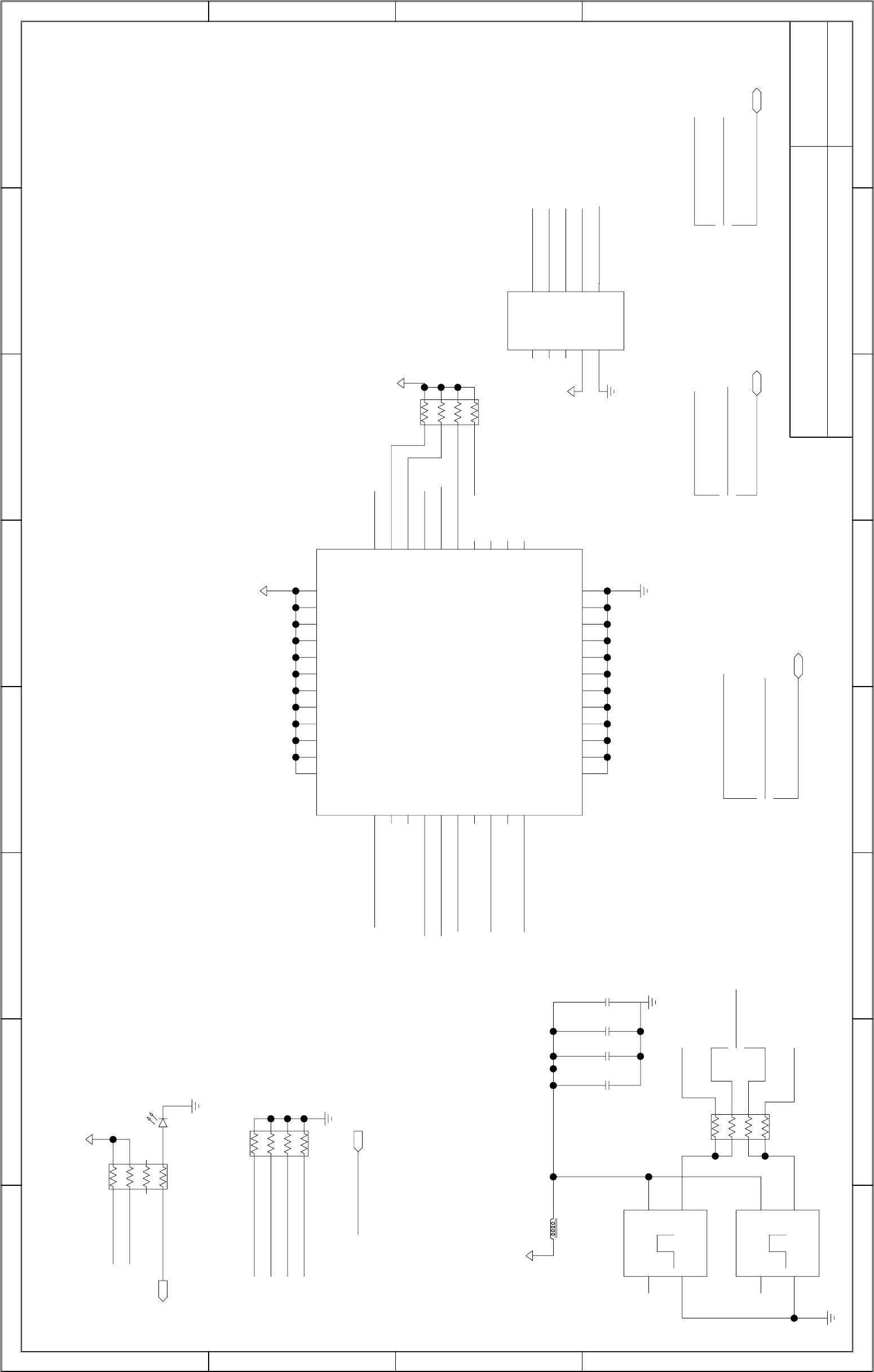

- 13. Additional Information/Resources

- 14. Component List

- 15. Schematics

DS3254 OR

ALTERNATE_MCLK:

REG CACR[AMCSEL1:0]=00 FOR 19.44MHZ

REG CACR[AMCSEL1:0]=10 FOR 77.76MHZ

BEGIN LIU HIERARCHY BLOCK

RST

LIU_ALT_MCLK

LIU_E3MCLK

44.736MHZ_3.3V

34.368MHZ_5.0V

.1UF

4.7UF

T3OSC

LIU_T3MCLK

E3_MCLK_IO

E3OSC

LIU_ALT_MCLK

LIU_T3MCLK

LIU_E3MCLK

LUI_HW

10K

330

RED

E3OSC

30

1UH

JTRST

10K

LIU_TEST

JTDO

JTRST

JTDO

JTDI

OSCSEL

JTDI

JTMS

JTMS

JTCLK

LIU_T3MCLK

.1UF

T3OSC

4.7UF

LIU_E3MCLK

ALE

MOT

LUI_HW

RST

INT

LIU_TEST

JTCLK

OSCSEL

LIU_ALT_MCLK

ALTERNATE_MCLK

9B3^ 9B3^

9B3^

T3_MCLK_IO

U07

E12

J8

E9

E4

H4

J4

D5

D4

B3

C11

K2

L10

D9

J9

H1

M8

A5

D8

H9

J5

D6

H7

H8

J7

E5

E6

F4

F5

F6

G7

G8

G9

D7

H5

H6

J6

E7

E8

F7

F8

F9

G5

G4

G6

DS19

1

2

YB03

4 5

1

8

YB04

4 5

1

8

L02

C10

C09

C07

C14

JP15

1

3

2

JP18

1

3

2

JP19

1

3

2

JP17

1

3

2

RP09

4

3

2

1

5

6

7

8

RPB40

4

3

2

1

5

6

7

8

J32

1

2

3

4

5 6

7

8

9

10

RPB55

4

3

2

1

5

6

7

8

RPB38

4

3

2

1

5

6

7

8

BLOCK NAME: _ds3154_liublock_dn. PARENT BLOCK: \_rc_top_dn_\

DS33M33DK01A0

20/26(TOTAL)

STEVE SCULLY

10/03/2007

1/3(BLOCK)

CR-46 : @\_rc_lib\.\_rc_top_dn_\(sch_1):page13_i204@\_rc_lib\.\_ds3154_liublock_dn\(sch_1):Page1

T3E3 LIU I/F. P.2,9,20-22

46B6 47A6

10B2^

47A647D8

10B2^

9B2^ 21A6

20C7

20C8 20A4

20C820B6

20A7

20C820C6

20A7

20B6 20A4

20C6 20A3

20B6

20A1

20B6

20A1

20C3

20B3

20B2

20A2

20B3

20B3

21B7

21B521B421B220A4

20B2

20C4

20B2

20B2

20C8 20A3

20A3

20C8

20A1

21C4

21D3

20C8

20B6

20B4

21B7

21B521B421B220A6

20C820B6

PAGE:

DATE:

TITLE:

ENGINEER:

A A

B B

C C

D

D

1

1

2

2

3

3

4

45

56

6

7

7

8

8

CONTROL

DS3154

VDD12

VDD2

VDD1VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VDD11

VDD10

VDD9

VDD8

VDD7

VDD6

VDD5

VDD4

VDD3

JTMS

JTCLK

JTDI

JTDO

HIZ

NC1

NC2

NC3

NC4

T3MCLK

E3MCLK

RST*

TCINV

TEST*

RCINV

STMCLK

TBIN

HW

RBIN

JTRST*

V3_3

V3_3

V3_3

OUT

V3_3

1

VCC

5

TDI

CONN_10P

GND

TDO

TMS

TCK

3

RST

IO IO

IN

IO

V3_3

VCC

1

OSC

GND OUT

VCC

1

OSC

GND OUT