Specifications

Table Of Contents

- Table of Contents

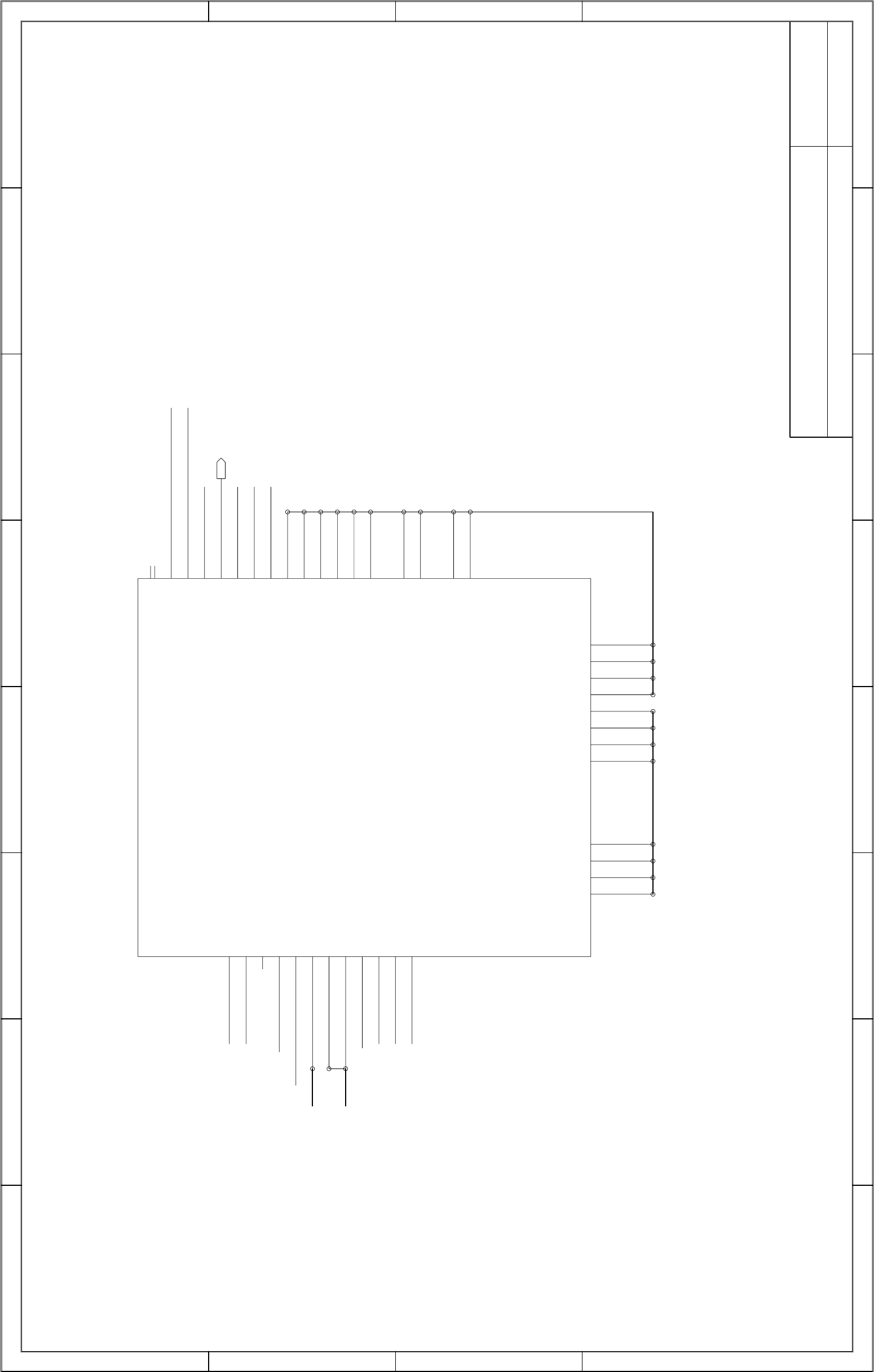

- 1. Board Floorplan

- 2. PCB Errata

- 3. File Locations

- 4. Basic Operation

- 5. Jumpers and Connectors

- 6. Line-Side Connections

- 7. System Connectors

- 8. Microcontroller

- 9. Power-Supply Connectors

- 10. Connecting to a Computer

- 11. Installing and Running the Software

- 12. Address Map

- 13. Additional Information/Resources

- 14. Component List

- 15. Schematics

CS_X1

RD_DS

WR_RW

ALE_DUT

1A8^

2

CPUCLK_OUT

PD<31..16>

22

16

15

1

3

6

5

4

3

2

1

13

12

11

10

6

4

8

7

5

9

0

D_DUT<7..0>

7

0

97_IO

CS_X3

ENABLE_DRV

ENABLE_CLBK

CS_X2

INT4

PROC_OSCIN

KIT_STATUS

INT2

MEM_SO

PA<19..0>

A_DUT_<13..0>

INT3

U08

124

103

101

100

99

98

97

96

92

91

84

82

80

108

107

134

131

130

129

126

125

123

122

121

119

118

116

115

114

113

112

111

110

109

144

143

141

140

137

136

93

BLOCK NAME: _motprocrescard_dn. PARENT BLOCK: \_rc_top_dn_\

5/6(BLOCK)

10/03/2007

STEVE SCULLY

DS33M33DK01A0

31/39(TOTAL)

CR-17 : @\_RC_LIB\.\_RC_TOP_DN_\(SCH_1):PAGE2_I10@\_RC_LIB\.\_MOTPROCRESCARD_DN\(SCH_1):PAGE5

MICROPORT. P.1,13-18

127

104

1A8^

14C1

1A8^

14C1

1A8^

14C1

14A8 14A5

13A1

1B8^

13A7

14D2

1A8^

14C1

13A715C8

14D1

1A8^

1B8^

14C1

1A8^

14B1

14C1

14C1

1A8^

14D2

PAGE:

DATE:

TITLE:

ENGINEER:

A A

B B

C C

D

D

1

1

2

2

3

3

4

45

56

6

7

7

8

8

OUT

LATTICE FPGA

BANK 2

BANK 3/8

BANK 1

BANK 0

LFE2-6-T144

PR16B (VREF2_3)

PR16A (VREF1_3)

PR17B (RLM0_GDLLC_IN_A**)

PR17A (RLM0_GDLLT_IN_A**)

PR26A (D6)

PR25B (D7) SPI_MOSI

PR29A (D0)

PR15A (PCLKT3_0)

PR15B (PCLKC3_0)

PR20A (RLM0_GPLLT_IN_A**)

PT12B(PCLKC1_0)

PT14A

PT14B

PT16A

PT18A

PT18B

PT20A

PT20B

PT22A

PT22B

PT24A

PT24B

PT26A

PT26B

PT28A(VREF1_1)

PT28B(VREF2_1)

PR13B (PCLKC2_0)

PR13A (PCLKT2_0)

PR2A (VREF1_2)

PR2B (VREF2_2)

PT10B(PCLKC0_0)

PT10A(PCLKT0_0)

PT6B

PT6A

PT4B

PT4A

PT2B (VREF2_0)

PT2A (VREF1_0)

PT12A(PCLKT1_0)

RLM0_PLLCAP

PR20B (RLM0_GPLLC_IN_A**)

NC

NC