Specifications

Table Of Contents

- Table of Contents

- 1. Board Floorplan

- 2. PCB Errata

- 3. File Locations

- 4. Basic Operation

- 5. Jumpers and Connectors

- 6. Line-Side Connections

- 7. System Connectors

- 8. Microcontroller

- 9. Power-Supply Connectors

- 10. Connecting to a Computer

- 11. Installing and Running the Software

- 12. Address Map

- 13. Additional Information/Resources

- 14. Component List

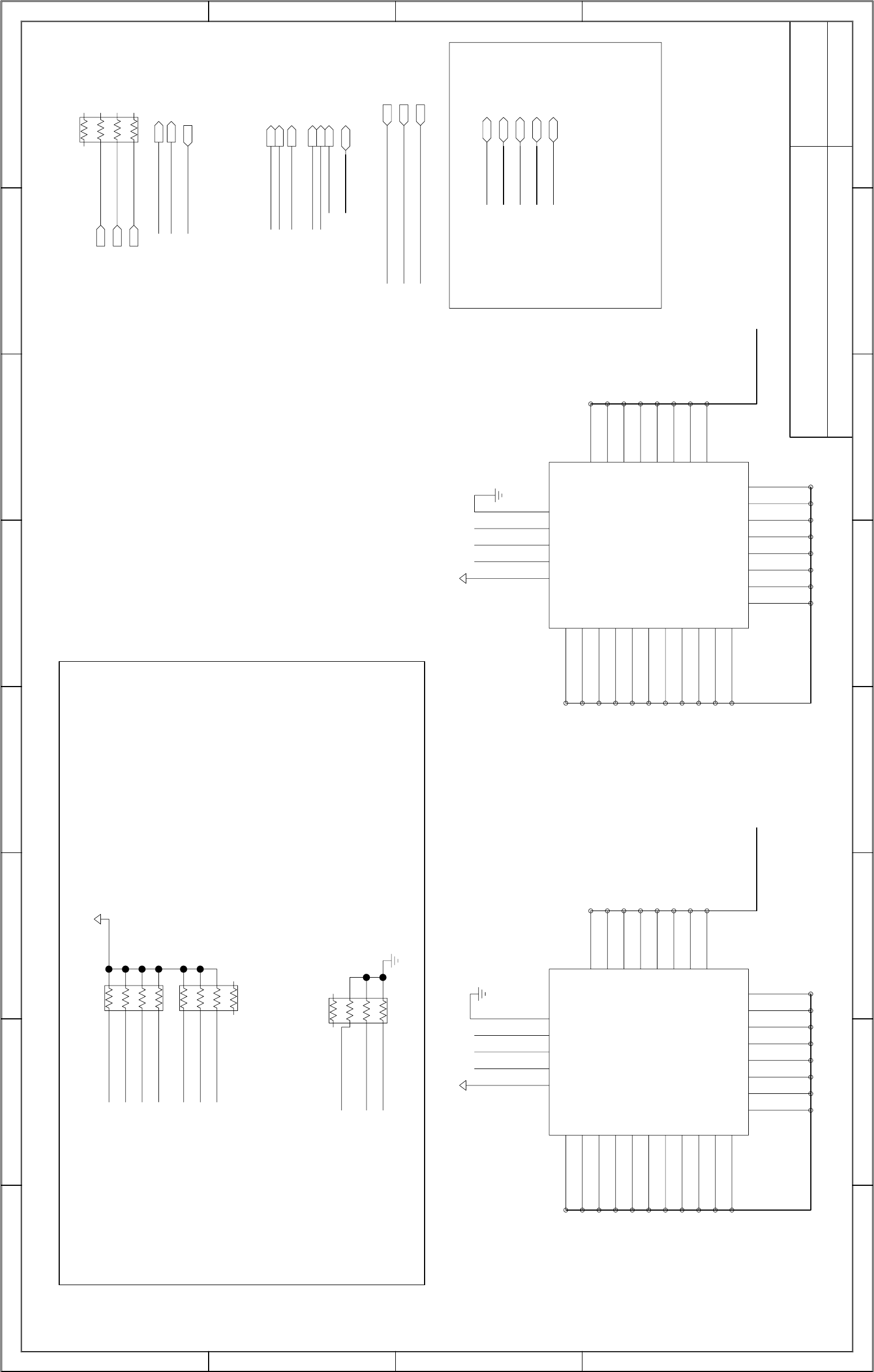

- 15. Schematics

(NOT USED IN THIS DESIGN)

NULL NETS

D18 HAS A 10K LOAD TO GND

WHEN SET FOR

MASTER MODE

FLASH ENABLE

INTERNAL

FULL DRIVE

BOOT INTERNAL

XTAL W/ PLL

RESET CONFIGURATION

BOOT

INTERN/EXTERN

19

18

RESET_OUT

RESET_IN

INT4

INT2

10K

I219

D_DUT<7..0>

ENABLE_DRV

CS_X1

WR_RW

MISC_IO<8..1>

MISC_IO<9>

RD_DS

CS_X2

CS_X3

15

PD<31..24>

24

25

22

CS0

OE

EB1

PD<23..16>

20

17

16

3

1

2

4

5

6

I203

19

18

17

16

10

9

7

8

PA<19..1>

26

27

28

29

30

31

CS0

OE

EB0

I142

18

19

16

17

15

6

5

4

2

1

3

7

13

14

11

12

10

9

PA<19..1>

8

CY62148V

PD<19>

PD<18>

10K

PD<28>

PD<23>

PD<22>

10K

PD<16>

PD<26>

PD<17>

PD<21>

10K

RCON

A_DUT_<13..0>

23

21

MISC_IO<10>

MISC_IO<11>

MISC_IO<12>

ENABLE_CLBK

CY62148V

EN_SOURCE_TIME

PROC_OSCIN

INT3

1A8^16A3

1A8^

18C215D513B5

1B8^ 17B7

1B8^ 17B7 13A7

1A8^17A5

17D3

1A8^17C3

1A8^17C3

1A8^17C3

1A8^

17C7

1A8^

17C7

1A8^17A4

17D3

17C3

1A8^

17C7

1B8^ 17C7

14

13

12

11

RPB61

4

3

2

1

5

6

7

8

RPB62

4

3

2

1

5

6

7

8

RPB57

4

3

2

1

5

6

7

8

U12

12

11

23

25

4

28

3

31

2

1

30

10

9

8

7

6

5

27

26

22

16

13

14

15

17

18

19

20

21

24

32

29

U11

12

11

23

25

4

28

3

31

2

1

30

10

9

8

7

6

5

27

26

22

16

13

14

15

17

18

19

20

21

24

32

29

RPB56

4

3

2

1

5

6

7

8

14/26(TOTAL)

STEVE SCULLY

10/03/2007

2/6(BLOCK)

BLOCK NAME: _motprocrescard_dn. PARENT BLOCK: \_rc_top_dn_\

CR-14 : @\_RC_LIB\.\_RC_TOP_DN_\(SCH_1):PAGE2_I10@\_RC_LIB\.\_MOTPROCRESCARD_DN\(SCH_1):PAGE2

DS33M33DK01A0

MICROPORT. P.1,13-18

16A1

14D714C713A2

16C414B713B5

16C414B713D3

16B4

13D7

16A114D714C7

13A2

16D4 14A8

13A1

16D4 14A5

13A1

16A1

14A2 13A2

16A1

14A5 13A2

16A1

14A2 13A2

16A1

14A2 13A2

16A1

14A2 13A2

16A1

14A5 13A2

16A1

14A2 13A2

16A1

14A2 13A2

13D3

PAGE:

DATE:

TITLE:

ENGINEER:

A A

B B

C C

D

D

1

1

2

2

3

3

4

45

56

6

7

7

8

8

V3_3

V3_3

OUT

OUT

IN

IN

IN

IN

IN

CY62148V

4-MBIT

(512K X 8)

IO3

IO2

IO0

IO1

IO6

IO5

IO4

IO7

GND

CE1*

VCC

A17

A18

WE*

OE*

A16

A15

A8

A9

A10

A11

A12

A13

A14

A0

A1

A2

A3

A4

A5

A6

A7

CY62148V

4-MBIT

(512K X 8)

IO3

IO2

IO0

IO1

IO6

IO5

IO4

IO7

GND

CE1*

VCC

A17

A18

WE*

OE*

A16

A15

A8

A9

A10

A11

A12

A13

A14

A0

A1

A2

A3

A4

A5

A6

A7

IO

IO

IO

IO

IO

IO

OUT

OUT

OUT

IN

OUT

OUT

OUT

IN

V3_3