Specifications

Table Of Contents

- Table of Contents

- 1. Board Floorplan

- 2. PCB Errata

- 3. File Locations

- 4. Basic Operation

- 5. Jumpers and Connectors

- 6. Line-Side Connections

- 7. System Connectors

- 8. Microcontroller

- 9. Power-Supply Connectors

- 10. Connecting to a Computer

- 11. Installing and Running the Software

- 12. Address Map

- 13. Additional Information/Resources

- 14. Component List

- 15. Schematics

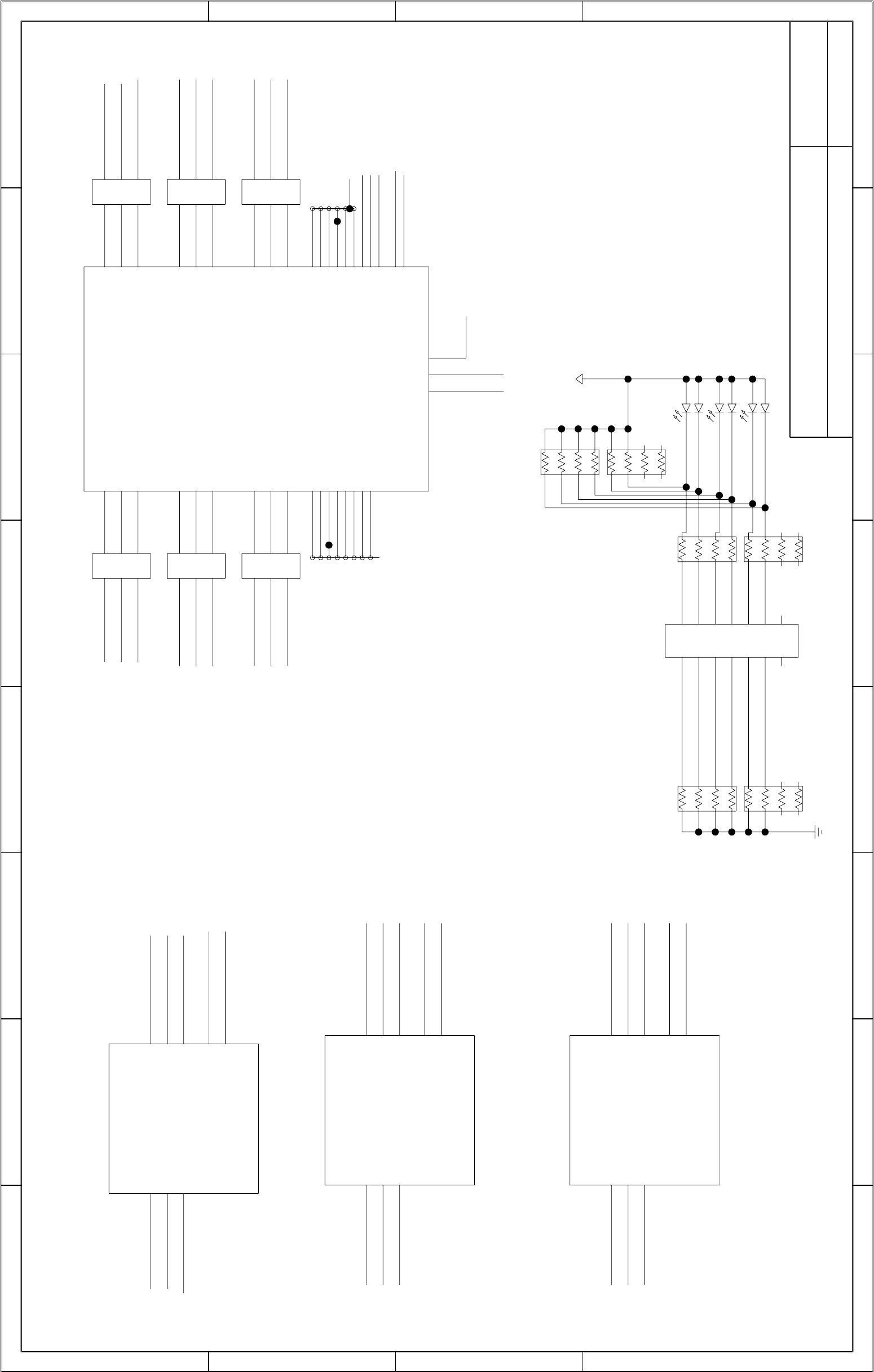

DATABUS TAPS WRONG [0:7]

THIS HAS BEEN FIXED IN THE FPGA.

BUG FIX:

PCB REV 01A0 HAD THE

PLACE TESTPOINTS TO ALLOW LOOPBAK T--R

PORT / PIN ASSIGNMENTS

DS33M33_RCLK1 IS AT PIN F3

DS33M33_RCLK3 IS AT PIN J2

DS33M33_RCLK2 IS AT PIN H3

M33_TNEG3

M33_TPOS3

DATA[7..0]

TE3_INT

WR_RW

RD_DS

330

M33_TPOS1

M33_TCLK2

M33_TPOS2

ADDR[5..0]

RESET_SYS

5

4

3

2

1

330

M33_TNEG3

M33_RCLK3

M33_RNEG3

M33_TCLK3

M33_RPOS3

M33_TPOS3

M33_GPIOB3

M33_GPIOA3

M33_RCLK2

M33_RNEG2

M33_TCLK2

M33_RPOS2

M33_GPIOB2

M33_GPIOA2

M33_RCLK1

M33_RNEG1

M33_TCLK1

M33_RPOS1

M33_TPOS1

M33_GPIOB1

M33_GPIOA1

M33_TNEG1

M33_TNEG1

M33_TCLK1

M33_RNEG1

M33_RCLK1

M33_RPOS1

M33_RNEG2

M33_RCLK2

M33_RPOS2

M33_RNEG3

M33_RCLK3

M33_RPOS3

M33_TNEG2

1K

1K

10K

10K

M3X_CLKA

RED_GREEN

M33_GPIOB1

M33_GPIOA1

M33_GPIOA3

M33_GPIOB3

M33_GPIOA2

M33_GPIOB2

M33_TCLK3

0

1

2

3

4

5

6

7

M33_TNEG2

M33_TPOS2

M3X_CLKB

TE3_L_CS

0

M3X_CLADCLK_TO_LIU

RED_GREEN

RED_GREEN

J12

1

2

3

4

5 6

J14

1

2

3

4

5 6

J17

1

2

3

4

5 6

J18

1

2

3

4

5 6

J15

1

2

3

4

5 6

J13

1

2

3

4

5 6

U05

G2

F2

F3

G4

E2

E3

F4

D2

U05

L4

K3

J2

K4

J3

J4

J5

K5

U05

H5

J6

H3

H4

H2

G3

H6

G5

RPB05

4

3

2

1

5

6

7

8

RPB02

4

3

2

1

5

6

7

8

DS07

1

2

3

4

DS06

1

2

3

4

DS01

1

2

3

4

RPB07

4

3

2

1

5

6

7

8

RPB04

4

3

2

1

5

6

7

8

J01

1

2

3

4

5 6

7

8

9

10

11

12

13 14

RPB13

4

3

2

1

5

6

7

8

RPB08

4

3

2

1

5

6

7

8

9/26(TOTAL)

CR-26 : @\_RC_LIB\.\_RC_TOP_DN_\(SCH_1):PAGE1_I9@\_RC_LIB\.\_DS33M30DK_DN_\(SCH_1):PAGE7

04/15/2007

9/12(BLOCK)

CR-9 : @\_RC_LIB\.\_RC_TOP_DN_\(SCH_1):PAGE9

STEVE SCULLY

DS33M30M31M33EE01A0

T3E3 LIU I/F. P.2,9,20-22

BLOCK NAME: _rc_top_dn_.

9A6

9A6

21D7v21D3v21C8v

21C7v21C3v21C2v8D68D48D38C68B3

1A8

10B5

1B1

20D8v

1B8

21C8v

1D31A8

10B5

8C1

21C4v

1D31A8

10B5

8C1

9D6

9C6

9B6

21D6v21D2v

21C6v21C3v21C2v

8B5

1A8

10B5

1A2

20B5v

1B51A8

11B310B4

9C4

9C1

9C1

9C4

9C1

9C4

10C49A5

10C49A5

9D1

9D1

9D4

9C1

10C49A5

10C49A5

9D1

9D1

9D4

9D1

9D4

10C49A5

10C49A5

9D4

9D6

9D6

9D8

9D8

9D8

9C8

9C8

9B8

9A8

9A8

9A8

9C6

20A3v10B7

1D3

9A6

9D4

9C4

20A2v10B7

1D2

21C4v

1A8

20A5v6C6

PAGE:

DATE:

TITLE:

ENGINEER:

A A

B B

C C

D

D

1

1

2

2

3

3

4

45

56

6

7

7

8

8

2

3

7

13

8

5

9

11

6

4

10

12

14

1

CONN_14P

2

1

3

4

2

1

3

4

2

1

3

4

V3_3

DS33M33_U

PORT

RLCLK

RNEG/RLCV

TLCLK

RPOS/RDAT TPOS/TDAT

GPIOB

GPIOA

TNEG

DS33M33_U

PORT

RLCLK

RNEG/RLCV

TLCLK

RPOS/RDAT TPOS/TDAT

GPIOB

GPIOA

TNEG

DS33M33_U

PORT

RLCLK

RNEG/RLCV

TLCLK

RPOS/RDAT TPOS/TDAT

GPIOB

GPIOA

TNEG

2

65

4

3

1

CONN_6P_U

2

65

4

3

1

CONN_6P_U

2

65

4

3

1

CONN_6P_U

2

65

4

3

1

CONN_6P_U

2

65

4

3

1

CONN_6P_U

2

65

4

3

1

CONN_6P_U

_ds3154_liublock_dn

HIERARCHY BLOCK

ADDR0

DATA7

DATA6

DATA5

DATA4

DATA3

DATA2

DATA1

DATA0

LIU_TPOS1

LIU_TNEG1

E3_MCLK_IO

T3_MCLK_IO

ALTERNATE_MCLK

RST

INT

RD_DS

CS

LIU_TCLK1

ADDR2

ADDR1

LIU_RPOS3

LIU_RNEG3

ADDR3

LIU_TNEG3

LIU_TCLK3

LIU_TPOS3

LIU_RCLK3

LIU_TPOS2

LIU_TCLK2

LIU_TNEG2

LIU_RPOS2

LIU_RCLK2

LIU_RNEG2

LIU_RPOS1

LIU_RCLK1

LIU_RNEG1

WR_RW

ADDR4

ADDR5