Specifications

Table Of Contents

- Table of Contents

- 1. Board Floorplan

- 2. PCB Errata

- 3. File Locations

- 4. Basic Operation

- 5. Jumpers and Connectors

- 6. Line-Side Connections

- 7. System Connectors

- 8. Microcontroller

- 9. Power-Supply Connectors

- 10. Connecting to a Computer

- 11. Installing and Running the Software

- 12. Address Map

- 13. Additional Information/Resources

- 14. Component List

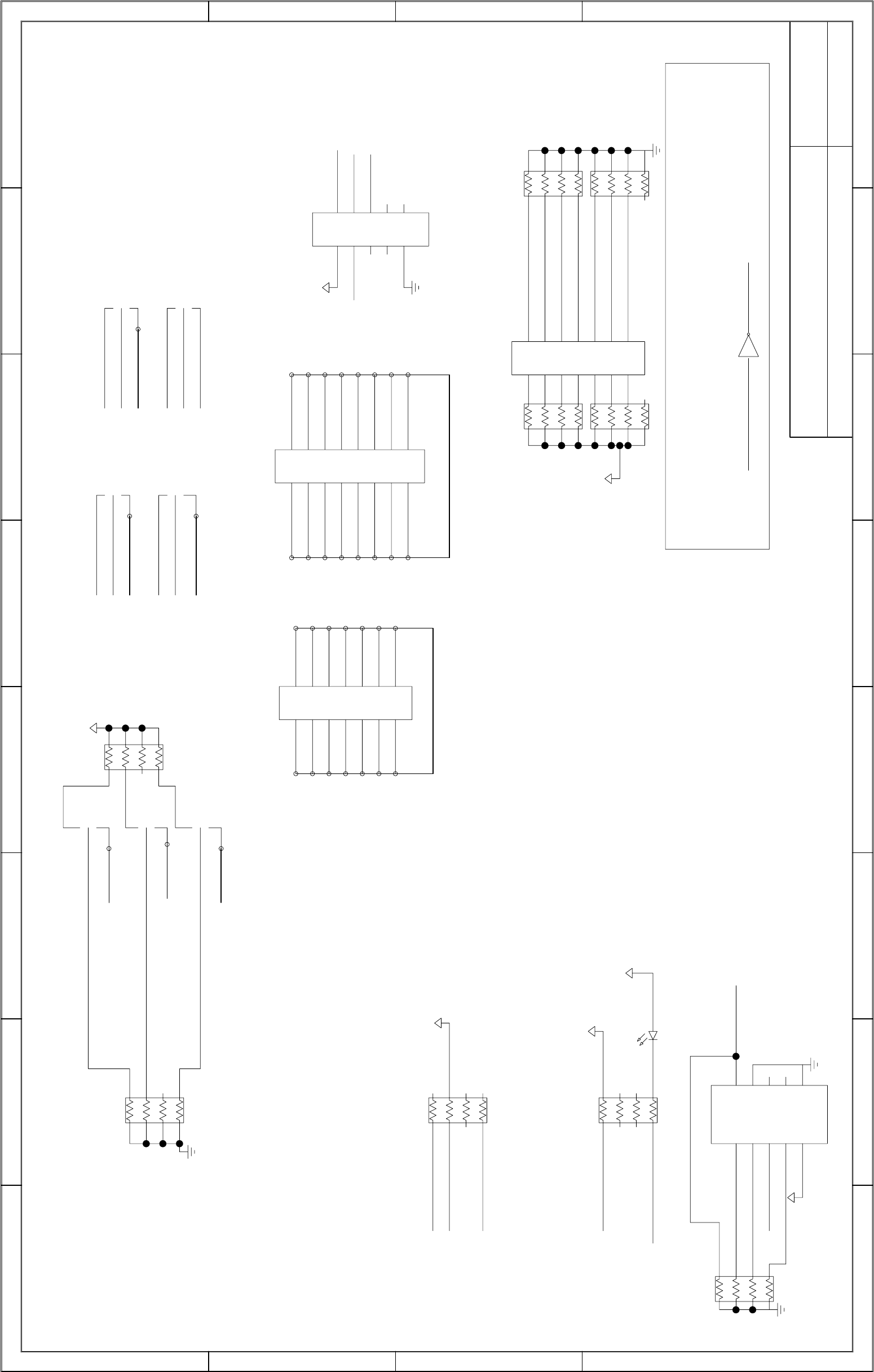

- 15. Schematics

REMOVE THIS INVERTER TO MAKE USE OF THE JUMPER OPTIONS FOR ALE (ABOVE)

AS TESTPOINTS FOR PROTO BOARD (NOT NEEDED)

INSTANTIATE PULLUP FOR INT IN FPGA

MT0 & MT2 ATTACED TO RPACK

DOUBLE CHECK BIAS NEEDS FOR MT1

ALE SHOULD BE TIED HIGH FOR NON-MULTIPLEXED ADDRESS

OPERATION AND TIED TIED LOW DURING SPI MODE (SPISEL=1).

M3X_JTMS

CS_X1

M3X_CS

JMP_3

13

M3X_CS

D2_SPI_CLK

DATA<7..0>

SPI_SS

2

JMP_3

INVERTER

M3X_INT

M3X_INT

RD_DS

13

WR_RW

5

1K

10K

1

DATA<7..0>

D7_SPI_CPOL

DATA<7..0>

DATA<7..0>

D0_SPI_MISO

SPI_SCK

7

6

5

1

0

JMP_3

10K

330

1K

10K

4

2

8

6

10

12

0

3

5

7

9

11

ADDR<13..0>

4

3

1

10

12

0

14

7

9

11

15

DATA<15..0>

2

8

6

D5_SPI_SWAP

10K

1K

D6_SPI_CPHA

M3X_MT0

M3X_MT1

M3X_MT2

M3X_ALE

M3X_RMIISEL

M3X_DCESEL

M3X_HIZ_N

M3X_SPISEL

M3X_TEST_EN

M3X_IFSEL_STYLE

M3X_IFSEL_SIZE

M3X_JTRST_N

M3X_SPISEL M3X_ALE

M3X_JTDI

M3X_JTDO

SPI_MISO

JMP_3

DATA<7..0>

D1_SPI_MOSI

SPI_MOSI

DATA<7..0>

1K

M3X_JTCLK

RPB50

4

3

2

1

5

6

7

8

J30

1

2

3

4

5 6

7

8

9

10

11

12

13 14

RPB52

4

3

2

1

5

6

7

8

RPB53

4

3

2

1

5

6

7

8

DS28

J16

1

2

3

4

56

7

8

9

10

RPB32

4

3

2

1

5

6

7

8

JP11

1

3

2

JP14

1

3

2

JP13

1

3

2

JP12

1

3

2

RPB36

4

3

2

1

5

6

7

8

JP22

1

3

2

JP21

1

3

2

JP20

1

3

2

RPB33

4

3

2

1

5

6

7

8

UB05

1

4

RPB49

4

3

2

1

5

6

7

8

RPB48

4

3

2

1

5

6

7

8

RPB29

4

3

2

1

5

6

7

8

J24

1

2

3

4

5 6

7

8

9

10

11

12

13 14

J21

1

2

3

4

5 6

7

8

9

10

11

12

13 14

15 16

J23

1

2

3

4

5 6

7

8

9

10

BIAS+CONFIG. P.8

CR-8 : @\_RC_LIB\.\_RC_TOP_DN_\(SCH_1):PAGE8

8/26(TOTAL)

8/12(BLOCK)

DS33M33DK01A0

STEVE SCULLY

10/03/2007

BLOCK NAME: _rc_top_dn_.

8C2

1A8

1D3 1A8

8D3

1B5

8D4 8C6

1D38C1

1D3 1B8

8A8

9C1

10B5

1A8 1D3

9C1

10B5

1A8 1D3

1B1

9C310B5

1A8

8B38C6

8D3

1B1

9C310B5

1A8

8B38D38D48D6

1B1

1B1

9C310B5

1A8

8B38C68D3

8D6

9C310B5

1A8

8B38C6

8D38D48D6

1B1

9C310B5

1A8

8B38C68D38D48D6

1B1

9C3

1A8

8B3

1C1

1A5

1A29C1

10B5

1A8

1B1

9C310B5

1A8

8C68D38D48D6

1C1

1C1

1B5

1B5

1B5

8A2

1A8

1D3

5A4

1B5

1C5

8A2

1B5

8B2

1A8 1D3

1C5

1D3

1A5

10B5

8D6

1B5

8D6 8D4

1C1

1C1

1C5

1C5

1C5

1B8

8D4

1B1

PAGE:

DATE:

TITLE:

ENGINEER:

A A

B B

C C

D

D

1

1

2

2

3

3

4

45

56

6

7

7

8

8

V3_3

6

10

8

4

1

2

3

5

7

9

CONN_10P

CONN_16P

2

4

8

10

12

14

16

3

1

7

9

11

13

15

5 6

V3_3

2

3

7

13

8

5

9

11

6

4

10

12

14

1

CONN_14P

V3_3

V3_3

NC7SZ86_U

V3_3

V3_3

2

3

7

13

8

5

9

11

6

4

10

12

14

1

CONN_14P

V3_3

CONN_10P

5

3

1

7

TMS

TCK

TDI

TDO

VCC GND