Specifications

Table Of Contents

- Table of Contents

- 1. Board Floorplan

- 2. PCB Errata

- 3. File Locations

- 4. Basic Operation

- 5. Jumpers and Connectors

- 6. Line-Side Connections

- 7. System Connectors

- 8. Microcontroller

- 9. Power-Supply Connectors

- 10. Connecting to a Computer

- 11. Installing and Running the Software

- 12. Address Map

- 13. Additional Information/Resources

- 14. Component List

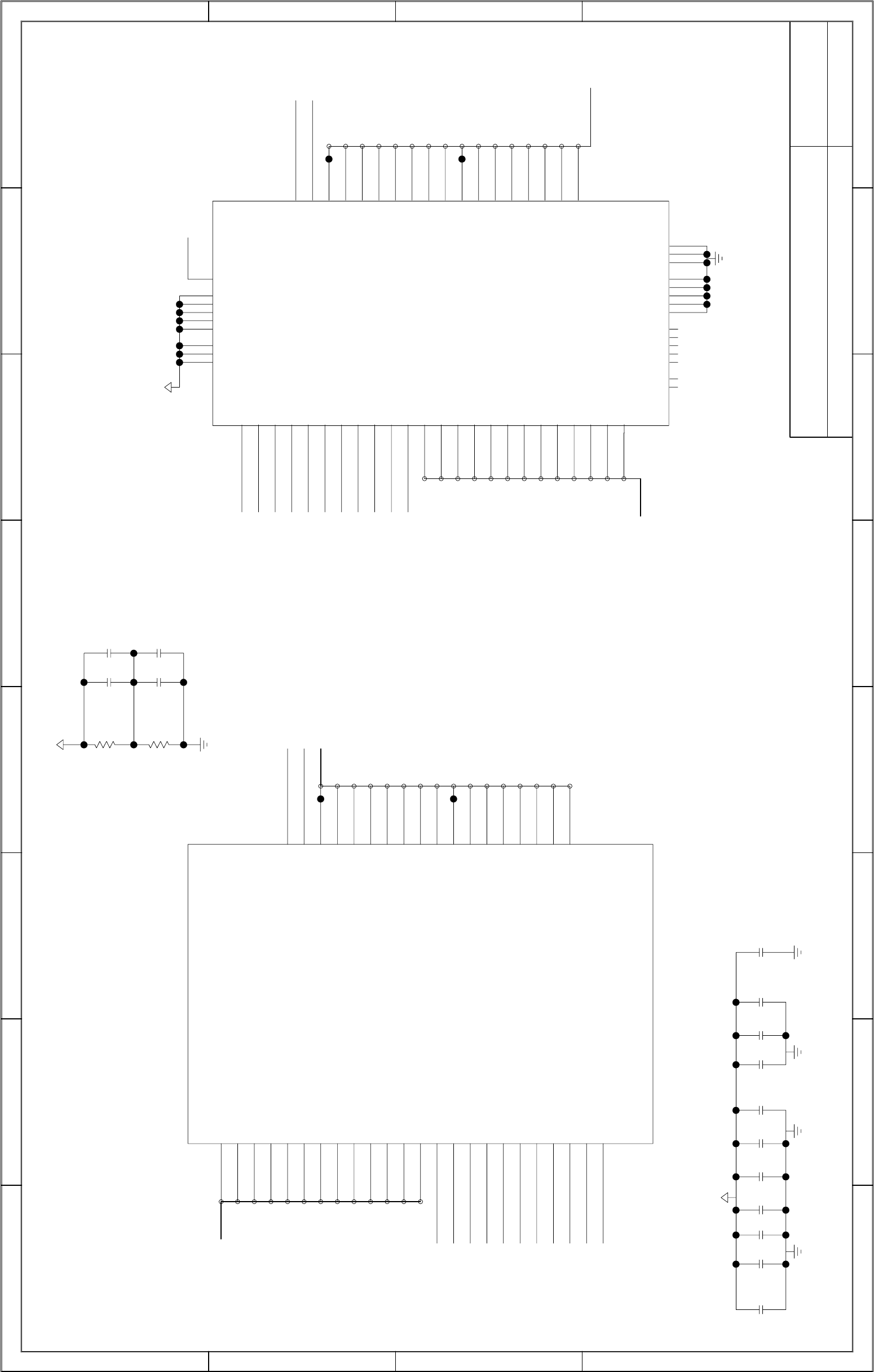

- 15. Schematics

FOR DDR

11

DDR_BA0

DDR_BA1

DDR_CAS

DDR_RAS

DDR_WE

DDR_CKE

DDR_CK

DDR_CS

DDR_CKINV

DDR_LDM

DDR_UDM

DDR_LDQS

DDR_UDQS

DDR_DQ<15..0>

DDR_DQ<15..0>

DDR_VREF

DDR_A<12..0>

DDR_VREF

4.7UF

4.7UF

.1UF

.1UF

.1UF

.1UF

4.7UF

4.7UF

12

10

9

8

7

6

5

4

3

2

1

0

0

1

2

3

5

4

6

7

8

9

10

11

12

14

13

15

1.00K 1.00K

.01UF .01UF

4.7UF 4.7UF

0

1

2

3

4

5

6

7

8

9

10

11

12

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

DDR_CS

DDR_CK

DDR_LDM

DDR_CKE

DDR_CKINV

DDR_CAS

DDR_BA0

DDR_BA1

DDR_RAS

DDR_WE

DDR_UDM

DDR_UDQS

DDR_LDQS

.01UF

.1UF

4.7UF

CB75CB76

CB72C08

RB12RB13

U06

29

28

41

42

30

31

32

35

36

37

38

39

40

26

27

22

45

46

44

24

50

19

2

57

59

60

62

63

65

4

5

7

8

10

11

13

54

56

20

16

17

43

14

25

53

23

47

51

1

18

33

55

3

15

9

61

49

66

48

34

52

64

58

12

6

21

CB58

CB102

CB49

CB90

CB83

CB85

CB146

CB89

CB74

CB110

CB63

U05

D12

C13

D13

C14

A14

B13

A13

A12

B11

C12

A11

B10

C11

D11

D9

B9

A9

A10

D10

C3

C4

D4

C5

D5

C6

D6

D7

A7

B6

A6

A5

B5

B4

A4

A3

B8

C7

C10

A8

B7

C9

B12

DDR_A<12..0>

10/03/2007

7/26(TOTAL)

7/12(BLOCK)

CR-7 : @\_RC_LIB\.\_RC_TOP_DN_\(SCH_1):PAGE7

DS33M33DK01A0

STEVE SCULLY

DDR MEMORY. P.7

BLOCK NAME: _rc_top_dn_.

7B8

7B8

7B8

7B8

7B8

7B8

7B8

7B8

7B8

7B8

7A8

7C5

7C5

7A4

7A1

7C4

10B3 7D2

7C8

10B37D5

7C3

7C3

7C3

7C3

7C3

7C3

7B3

7C3

7C3

7C3

7C3

7C1

7C1

PAGE:

DATE:

TITLE:

ENGINEER:

A A

B B

C C

D

D

1

1

2

2

3

3

4

45

56

6

7

7

8

8

SDRAM I/F

DS33M33_U

SDUDM

SDWE*

SDRAS*

SDBA[1]

SDBA[0]

SDA[1]

SDA[0]

SDA[4]

SDA[3]

SDA[2]

SDA[6]

SDA[5]

SDA[9]

SDA[7]

SDA[8]

SDA[11]

SDA[10]

SDA[12]

SDCAS*

SDCLKN

SDCLKEN

SDLDM

SDCLKP

SDCS* SDDQ[0]

SDDQ[2]

SDDQ[1]

SDDQ[3]

SDDQ[5]

SDDQ[4]

SDDQ[6]

SDDQ[7]

SDDQ[8]

SDDQ[9]

SDDQ[10]

SDDQ[11]

SDDQ[12]

SDDQ[13]

SDDQ[14]

SDDQ[15]

SDUDQS

SDLDQS

V2_5

MT46V16M16BG75

A8

A9

A10/AP

A11

A12

A1

A2

A3

A4

A5

A6

A7

BA0

BA1

CAS

RAS

WE

CKE

CK

CS

CK_INV

LDM

UDM

DNU

DNU

NC

NC

NC

NC

NC

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VREF

A0

DQ0

DQ1

DQ3

DQ2

DQ6

DQ4

DQ5

DQ7

DQ8

DQ9

DQ11

DQ10

DQ13

DQ14

DQ12

LDQS

DQ15

UDQS

V2_5

V2_5