Specifications

Table Of Contents

- Table of Contents

- 1. Board Floorplan

- 2. PCB Errata

- 3. File Locations

- 4. Basic Operation

- 5. Jumpers and Connectors

- 6. Line-Side Connections

- 7. System Connectors

- 8. Microcontroller

- 9. Power-Supply Connectors

- 10. Connecting to a Computer

- 11. Installing and Running the Software

- 12. Address Map

- 13. Additional Information/Resources

- 14. Component List

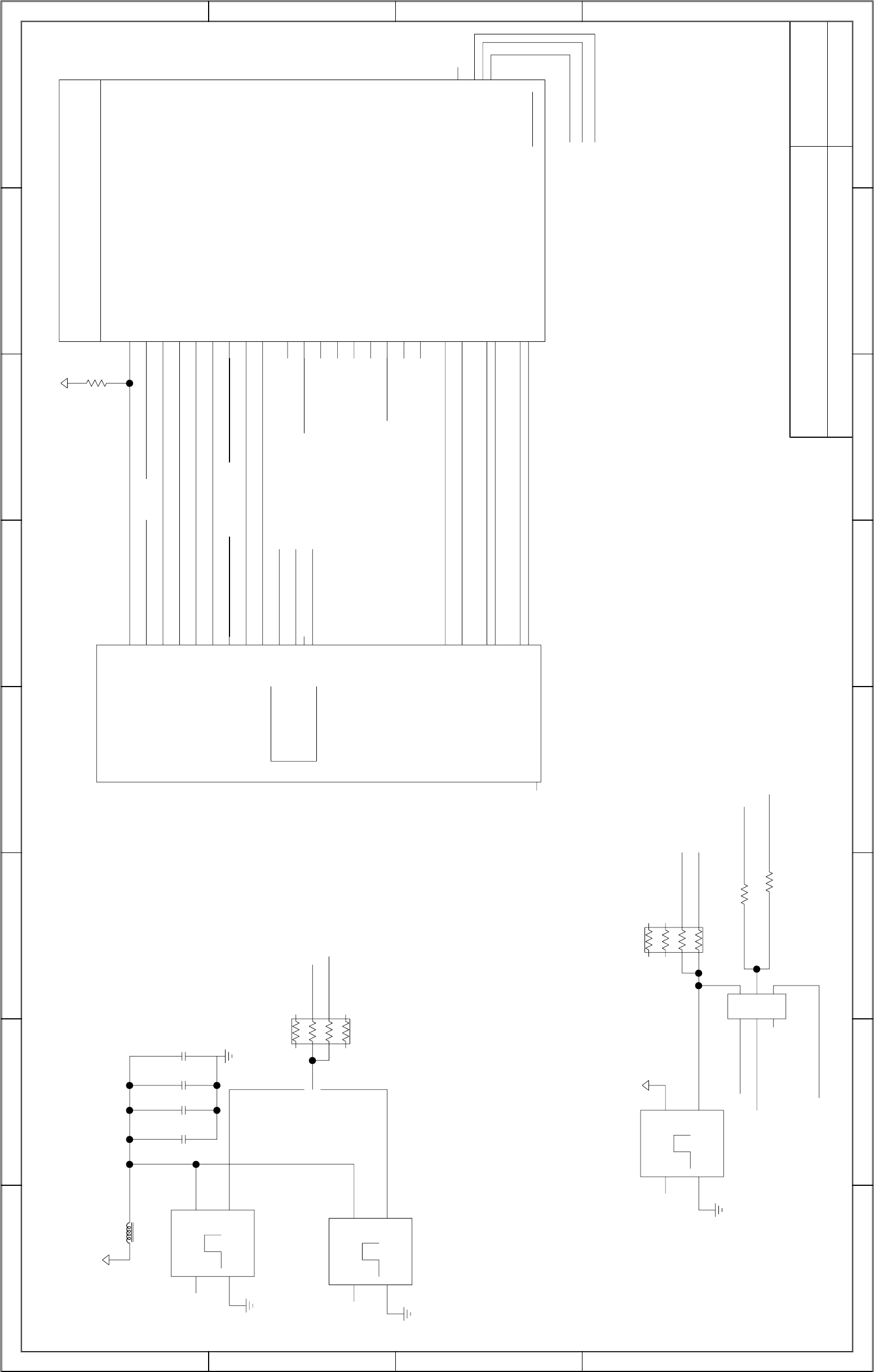

- 15. Schematics

USED IN RMII MODE (50 MHZ)

ETH_REF_CLK IS ONLY

CLKA AND CLKB TESTPOINTS ARE IN THE LIU BLOCK

REFCLK & CLKC TESTPOINTS ARE IN THE PHY BLOCK

CLOCK TESTPOINTS:

NOT CONNECTION TO A RESOURCE CARD

IS INTENDED FOR USE AS TESTPOINTS

ETHERNET CONNECTOR (I.M. BUS)

25MHZOSC_TO_PROC

ETH_TXD<7..0>

CLK_TO_MAC

GTXCLK

ETH_COL_DET

ETH_RXD<7..0>

GMII_TX_ER_

I23

I24

1UH

4.7UF

.1UF

M3X_CLADCLK_TO_LIU

30

I22

2.2K

30

30

25.000MHZ_3.3V_SOCKET

CLK_TO_MAC

AV_LAN_CLK

PY25MHZOSC

M3X_LAN_CLKO

M3X_CLKC

REFC_25M

JMP_3

M3X_CLADCLK

GMII_TX_ER_

19.44MHZ_3.3V_SOCKET

4.7UF

.1UF

77.76MHZ_3.3V_SOCKET

CLK_TO_MAC

GTXCLK

AV_LAN_CLK

ETH_RXD<7..4>

ETH_TXD<7..4>

RESET_LAN

ETH_RXD<3..0>

ETH_RX_CLK

ETH_RXDV

ETH_RX_CRS

ETH_RX_ERR

ETH_TXD<3..0>

ETH_TX_CLK

ETH_TX_EN

ETH_MDIO

ETH_MDC

PY25MHZOSC

PHY_INT

M3X_LAN_CLK

30

RB08

YB02

4 5

1

8

JP01

1

3

2

RB15

RB14

YB01

4 5

1

8

YB05

4 5

1

8

J19

1

2

3

4

5 6

RP13

4

3

2

1

5

6

7

8

RPB23

4

3

2

1

5

6

7

8

L01

C01

C02

C03

C04

6/26(TOTAL)

STEVE SCULLY

6/12(BLOCK)

10/03/2007

CR-6 : @\_RC_LIB\.\_RC_TOP_DN_\(SCH_1):PAGE6

DS33M33DK01A0

ETHERNET. P.5-6,19,25-26

BLOCK NAME: _rc_top_dn_.

6B1

25A7v

19B3v

25B1v19B3v

6A7

25B7v

19B3v6A1

5A4

19C3v 5A525A1v

6B1

5C6

9B2

25B1v

19B3v 6B1

6C3

5A4

19B3v6B4

1A8

25B4v6B4

5A4

10B7

1D2

10B71D3

25A7v

19B3v

6C4 5C6

25B7v

19B3v

5A4 6C4

25B1v

19B3v

6C3 6A7

6C45B6

19B3v

25B7v

5B26D3

19C3v

25B7v

5C3

19C3v25A1v

5A5

19C3v25A1v

5C3

19B3v25A1v

6C45B6

19C3v

25B7v

19B3v

PAGE:

DATE:

TITLE:

ENGINEER:

A A

B B

C C

D

D

1

1

2

2

3

3

4

45

56

6

7

7

8

8

VCC

1

OSC

GND OUT

SINGLE 50 PIN

FOR CONNECTION TO ETHERNET CARD

USED ON BOTTOM OF MOTHERBOARD

CONNECTORS

ETHERNET (LAN)

I.M. CARD PLUG-CONNECTORS

HIERARCHY BLOCK

_phy_imbus_mb_dn

PHY_INT

OSC25M

MDC

MDIO

PT2_TX_EN

PT2_RX_CLK

PT2_COL_DET

PT1_TX_EN

PT1_TX_CLK

PT1_TXD<3..0>

PT1_RX_ERR

PT1_RX_CRS

PT1_RXDV

PT1_RX_CLK

PT1_COL_DET

PT1_RXD<3..0>

GMII_TX_ER_

GMII_CLKTOMAC_BUF

SPARE

GMII_CLKFROM_MAC

RESET_B

PT2_TX_CLK

PT2_TXD<3..0>

PT2_RX_ERR

PT2_RX_CRS

PT2_RXDV

PT2_RXD<3..0>

LAN_CLK

V3_3

GMII

ONLY

_phy_dp83865bvh_dn

HIERARCHY BLOCK

SPARE<4..1>

CLKTOMAC_TESTPNT

CLKTOMAC

GMII_CLKFROM_MAC

COL_DET

RX_ERR

PHY_INT

RXD<7..0>

TXD<7..0>

RXDV

RX_CLK

RX_CRS

TX_CLK

TX_EN

TX_ER_

RESET_B

MDIO

MDC

PHYOSC25M

LAN_CLK

2

65

4

3

1

CONN_6P_U

VCC

1

OSC

GND

OUT

VCC

1

OSC

GND OUT

V3_3

V3_3