Specifications

Table Of Contents

- Table of Contents

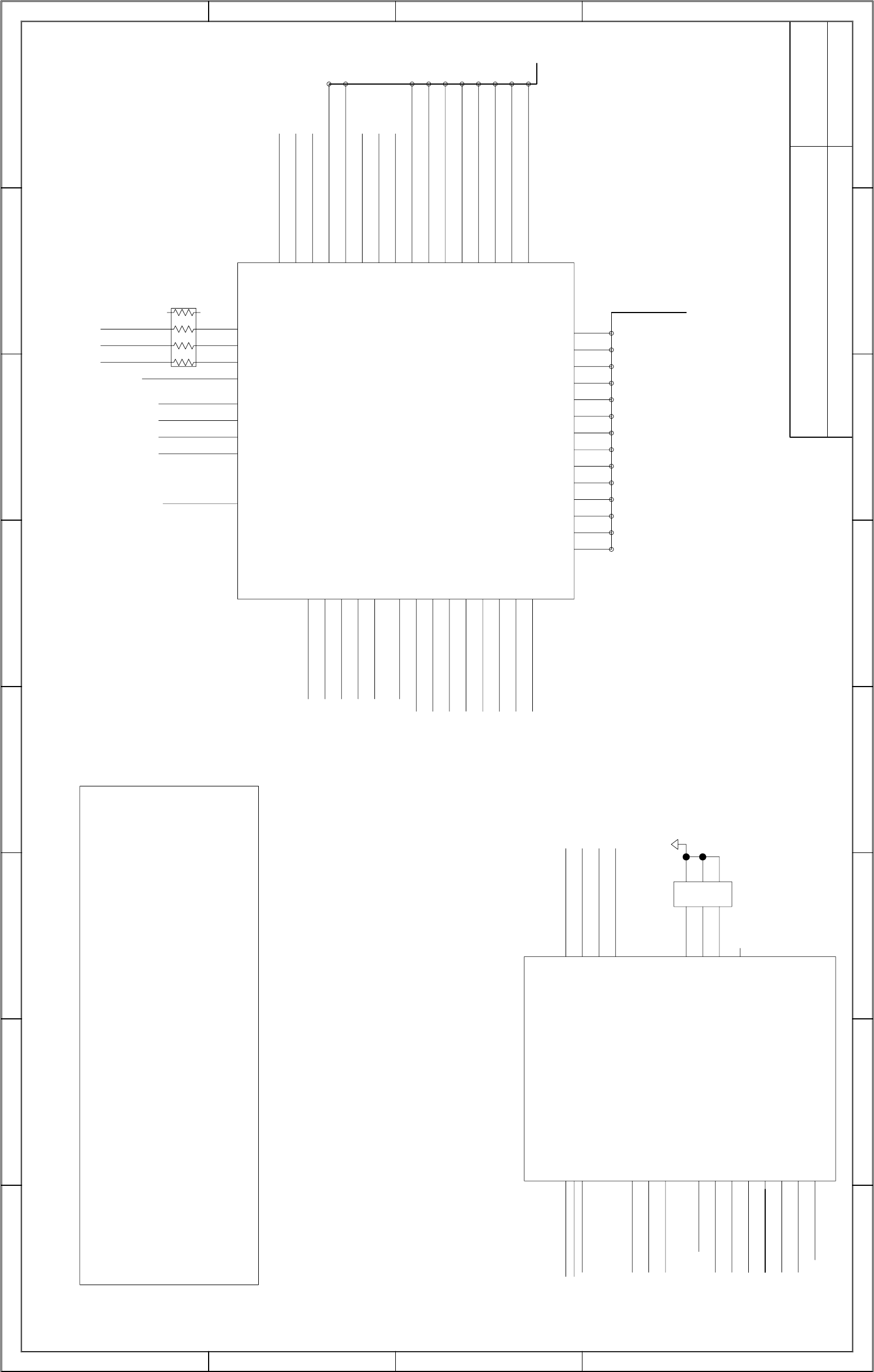

- 1. Board Floorplan

- 2. PCB Errata

- 3. File Locations

- 4. Basic Operation

- 5. Jumpers and Connectors

- 6. Line-Side Connections

- 7. System Connectors

- 8. Microcontroller

- 9. Power-Supply Connectors

- 10. Connecting to a Computer

- 11. Installing and Running the Software

- 12. Address Map

- 13. Additional Information/Resources

- 14. Component List

- 15. Schematics

BEGINNING OF DS33M33DK

DS33M33DK CONTENTS / INDEX

ADDR<13..0>

DATA<7..0>

WR_RW

RD_DS

M3X_ALE

CPLD_CS

SPI_MISO

SPI_SCK

M3X_HIZ_N

N6

M3X_IFSEL_STYLE

M3X_IFSEL_SIZE

D6_SPI_CPHA

D2_SPI_CLK

DATA<15..0>

15

14

12

13

9

10

11

8

0

1

2

3

4

5

6

7

8

9

10

11

13

3

4

SPI_SS

TE3_INT

PHY_INT

RESET_LAN

RESET_SYS

30

12

25MHZOSC_TO_PROC

D5_SPI_SWAP

D1_SPI_MOSI

SPI_MOSI

M3X_JTRST_N

M3X_JTMS

M3X_JTCLK

M3X_JTDI

M3X_SPISEL

M3X_TEST_EN

M3X_MT0

M3X_MT1

M3X_MT2

M3X_INT

D7_SPI_CPOL

RESET_SYS

M3X_JTDO

M3X_CLADCLK

M3X_CLKC

M3X_CLKB

M3X_CLKA

M3X_ALE

WR_RW

RD_DS

M3X_CS

M3X_INT

J20

1

2

3

4

5 6

U05

L12

P13

M12

R13

N13

T13

R14

P14

T14

L13

R15

M13

N14

T15

N12

M3

L2

K2

L5

N8

N7

N9

N10

M9

M8

M7

M10

M11

L8

H11

H12

J11

L9

K12

B1

P7

N5

M4

N2

P2

N3

P1

N4

B2

A1

M2

M6

E14

C1

F5

M5

RPB34

4

3

2

1

5

6

7

8

D0_SPI_MISO

N11

ADDR<13..0>

TE3_L_CS

CS_X1

MICROPORT. P.1,13-18

DS33M33DK01A0

MICROPORT. P.1,13-18

DDR MEMORY. P.7

OSCILLATORS. P.6

BIAS+CONFIG. P.8

CR-1 : @\_RC_LIB\.\_RC_TOP_DN_\(SCH_1):PAGE1

ETHERNET. P.5-6,19,25-26

POWER. P.11-12

SERDES. P.3-4

STEVE SCULLY

1/26(TOTAL)

10/03/2007

1/12(BLOCK)

BLOCK NAME: _rc_top_dn_. PARENT BLOCK: <CON_PARENT_NAME>

OVERHEAD. P.2,10,23-24

T3E3 LIU I/F. P.2,9,20-22

8A2

8D4

8D4

8D7

8D3

13B7v

8D3

13B6v

8D3

13B6v

6B4

14D1v

6B416B3v

10B5

17C6v

9B1

10B411B3

1B5

13B6v

8C19C1

10B5

1D3

17C4v

9C1

17C6v

1B1

9C310B5

8B38C68D38D48D6

17A5v17A6v

1A29C1

10B5

8B517A5v17C4v

6A5

17C6v

8D7

8D4

13B7v

8A6

8A7

8A7

8A8

8A28A3

8A2

8A2

8A8

8B2

8B8

8B8

8B8

1D38C1

8A8

13B7v

8D7

9B1

10B411B3

1A813B6v

8A7

6C6 10B7

8B2

1D3

17C4v

6A7 10B7

9B2 10B7

9B2 10B7

8A2 8B2

1A8 17C4v

8C2 8D3

1A8

17C4v

8C1 1B8

8A8 13B7v

8D4

9C1

10B5

1A8

8B5 17A5v 17C4v

PAGE:

DATE:

TITLE:

ENGINEER:

A A

B B

C C

D

D

1

1

2

2

3

3

4

45

56

6

7

7

8

8

CONTROL

DS33M33_U

TEST

HIZ*

MT0

MT1

MT2

IFSEL[0]

IFSEL[1]

REFCLK

CLKB

CLKA

CLKC

D[15]

D[14]

D[13]

D[12]

D[11]

D[10]

D[8]

D[7]/CPOL

D[6]/CPHA

D[5]/SPISWAP

D[4]

D[3]

D[1]/SDI

D[2]/SCLK

ALE

INT*

CS*

D[9]

D[0]/SDO

RD*/DS*

WR*/R/W*

SPISEL

RST*

JTDO

JTDI

JTCLK

JTMS

JTRST*

A[0]

A[1]

A[2]

A[3]

A[4]

A[5]

A[6]

A[7]

A[8]

A[9]

A[10]

A[11]

A[12]

A[13]

V3_3

2

65

4

3

1

CONN_6P_U

_motprocrescard_dn

MICROPROCESSOR

HIERARCHY BLOCK

ALE_DUT

RD_DS

MISC_IO<12..1>

WR_RW

EN_SOURCE_TIME

ENABLE_DRV

SPI_MISO

SPI_SCK

SPI_CS

SPI_MOSI

A_DUT_<13..0>

CS_X1

INT2

D_DUT<7..0>

INT3

INT4

ENABLE_CLBK

CS_X2

CS_X3

RESET_IN

PROC_OSCIN

RESET_OUT