Owner's manual

14-6

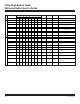

Ultra-High-Speed Flash

Microcontroller User’s Guide

IN STRUCTION CODE

MNE MO NIC

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

H EX B YTE C YCLE EXPLAN ATION

JC re l

0

r

7

1

r

6

0

r

5

0

r

4

0

r

3

0

r

2

0

r

1

0

r

0

40

B y t e 2

2 3

(PC) = (PC) + 2

IF (C) = 1 THEN

(PC) = (PC) + re l

JNC re l

0

r

7

1

r

6

0

r

5

1

r

4

0

r

3

0

r

2

0

r

1

0

r

0

50

B y t e 2

2 3

(PC) = (PC) + 2

IF (C) 0 THEN

(PC) = (PC) + re l

J B b it, re l

0

b

7

r

7

0

b

6

r

6

1

b

5

r

5

0

b

4

r

4

0

b

3

r

3

0

b

2

r

2

0

b

1

r

1

0

b

0

r

0

20

B y t e 2

B y t e 3

3 4

(PC) = (PC) + 3

IF (bit) = 1 THEN

(PC) = (PC) + re l

JN B b i t, rel

0

b

7

r

7

0

b

6

r

6

1

b

5

r

5

1

b

4

r

4

0

b

3

r

3

0

b

2

r

2

0

b

1

r

1

0

b

0

r

0

30

B y t e 2

B y t e 3

3 4

(PC) = (PC) + 3

IF (bit) = 0 THEN

(PC) = (PC) + re l

J B C b it, r e l

0

b

7

r

7

0

b

6

r

6

0

b

5

r

5

1

b

4

r

4

0

b

3

r

3

0

b

2

r

2

0

b

1

r

1

0

b

0

r

0

10

B y t e 2

B y t e 3

3 4*

(PC) = (PC) + 3

IF (bit) = 1 THEN

(bit) = 0 and (PC) =

(PC) + re l

C JNE A, d irect, re l

0

a

7

r

7

1

a

6

r

6

0

a

5

r

5

1

a

4

r

4

0

a

3

r

3

0

a

2

r

2

0

a

1

r

1

0

a

0

r

0

B5

B y t e 2

B y t e 3

3 5

(PC) = (PC) + 3

IF (direct) < ( A)

THEN (PC) = (PC)

+ r e l a nd (C) = 0

OR

IF (direct) > ( A)

THEN (PC) = (PC)

+ r e l a nd (C) = 1

C JNE A, #dat a, re l

1

d

7

r

7

0

d

6

r

6

1

d

5

r

5

1

d

4

r

4

0

d

3

r

3

1

d

2

r

2

0

d

1

r

1

0

d

0

r

0

B4

B y t e 2

B y t e 3

3 4

(PC) = (PC) + 3

IF #data < (A)

THEN (PC) = (PC)

+ r e l a nd (C) = 0

OR

IF #data > (A)

THEN (PC) = (PC)

+ r e l a nd (C) = 1

CJNE R n,

#data, r e l

1

d

7

r

7

0

d

6

r

6

1

d

5

r

5

1

d

4

r

4

1

d

3

r

3

n

2

d

2

r

2

n

1

d

1

r

1

n

0

d

0

r

0

B8-BF

B y t e 2

B y t e 3

3 4

(PC) = (PC) + 3

IF #data < (R n)

THEN (PC) = (PC)

+ r e l a nd (C) = 0

OR

IF #data > (R n)

THEN (PC) = (PC)

+ r e l a nd (C) = 1

CJNE @ Ri,

#data, r e l

1

d

7

r

7

0

d

6

r

6

1

d

5

r

5

1

d

4

r

4

0

d

3

r

3

1

d

2

r

2

1

d

1

r

1

i

d

0

r

0

B6-B7

B y t e 2

B y t e 3

3 5

(PC) = (PC) + 3

IF #data < ((Ri))

THEN (PC) = (PC)

+ r e l a nd (C) = 0

OR

IF #data > ((Ri))

THEN (PC) = (PC)

+ r e l a nd (C) = 1

DJNZ R n, re l

1

r

7

1

r

6

0

a

5

r

5

1

r

4

1

r

3

n

2

r

2

n

1

r

1

n

0

r

0

D8-Df

B y t e 2

3 4

(PC) = (PC) + 2

(Rn) = ( Rn) - 1

IF (Rn) 0 THEN

(PC) = (PC) + re l

D JNZ direct, r e l

1

a

7

r

7

1

a

6

r

6

1

d

5

r

5

1

a

4

r

4

0

a

3

r

3

1

a

2

r

2

0

a

1

r

1

1

a

0

r

0

D5

B y t e 2

B y t e 3

3 5

(PC) = (PC) + 3

(direct) = (direct) - 1

IF (direct) 0 THEN

(PC) = (PC) + re l

PROGRAM BRANCHING

NOP 0 0 0 0 0 0 0 0 00 1 1 (PC) = (PC) + 1

* Note: One additional clock cycle is required if the PSW, SP, DPS, IE, EIE, IP0, IP1, EIP0, or EIP1 register is accessed by certain direct

addressing instructions marked with an *. Additionally, the JBC bit instruction requires one additional clock cycle to clear a bit if the

jump is actually taken.

Maxim Integrated