Owner's manual

13-3

Timed-Access Protects Watchdog

Any microcontroller-based system can be faced with environmental conditions that are beyond its designed abilities. These include

external signal transients due to component failure, fluctuating power conditions, massive electrostatic discharge (ESD), and other

unexpected system events. When a microcontroller is exposed to such conditions, program execution can become corrupted. The

ultra-high-speed microcontroller incorporates a watchdog timer that can initiate a reset to recover from these conditions. The primary

function of the timed-access feature is to protect against accidental disabling of the watchdog timer by an “out-of-control” device. This

allows the watchdog timer to reset the system in the event of program execution failure.

The following hypothetical example demonstrates how a single bit change can corrupt program execution. The timed-access proce-

dure protects against an accidental write to the EWT bit by the errant code, allowing the watchdog timer reset function to reset the

device. While this is a purely fictitious example, it illustrates how the watchdog timer and timed-access feature allow the ultra-high-

speed microcontroller to minimize the effect of accidental code corruption. Note: Timed access is not optional and must be support-

ed if the protected bits are used. This example helps explain the category of problem that the timed access prevents.

EXAMPLE: A TRANSIENT CAUSES THE WATCHDOG TO BE DISABLED:

TABLE_READ:

C2D2 90 0A 00 MOV DPTR, 0A00H ;LOAD TABLE POINTER

C2D5 79 FF MOV R1, #0FFH

;LOAD COUNTER

C2D7 78 90 MOV R0, #90H ;DESTINATION POINTER

LOOP:

C2D9 E0 MOVX A, @DPTR ;READ DATA BYTE

C2DA F6 MOV @R0, A ;STORE IT IN RAM

C2DB 06 INC R0 ;NEXT TABLE LOCATION

C2DC A3 INC

DPTR ;NEXT DATA VALUE

C2DD D9 C2 D9 DJNZ R1, LOOP ;NEXT BYTE OR DONE ?

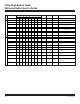

VALID TIMED-ACCESS PROCEDURES

Three Memory Cycles Three Memory Cycles Three Memory Cycles

MOV 0C7h, #0AAh MOV 0C7h, #55h SETB EWT

Three Memory Cycles Three Memory Cycles One Memory Cycle Two Memory Cycles

MOV 0C7h, #0AAh MOV 0C7h, #55h NOP SETB EWT

Three Memory Cycles Three Memory Cycles Three Memory Cycles

MOV 0C7h, #0AAh MOV 0C7h, #55h MOV WDCON, #02h

INVALID TIMED-ACCESS PROCEDURES

Three Memory Cycles One Memory Cycle Three Memory Cycles Two Memory Cycles

MOV 0C7h, #0AAh NOP MOV 0C7h, #55H SETB EWT

*Second write to TA register does not occur within 3 cycles of first write.

Three Memory Cycles Three Memory Cycles One Memory Cycle Three Memory Cycles

MOV 0C7h, #0AAh MOV 0C7h, #55H NOP MOV WDCON, #02h

*Modification of protected bit did not occur with 3 cycles of second write to TA register.

Three Memory Cycles Three Memory Cycles Two Memory Cycles Two Memory Cycles

MOV 0C7h, #0AAh MOV 0C7h, #55h SETB EWT SETB EWT

*Modification of second protected bit did not complete within 3 cycles of second write to TA

register.

Figure 13-1. Timed-Access Examples

Ultra-High-Speed Flash

Microcontroller User’s Guide

Maxim Integrated