Datasheet

MAX1280/MAX1281

400ksps/300ksps, Single-Supply, Low-Power, 8-Channel,

Serial 12-Bit ADCs with Internal Reference

6 _______________________________________________________________________________________

V

DD1

=

V

DD2

= 3.6V

I

SOURCE

= 0.5mA

CONDITIONS

mA

2.5 3.5

I

VDD1

+

I

VDD2

Supply Current (Note 10)

V2.7 3.6

V

DD1

,

V

DD2

VV

DD2

- 0.5VV

OH

Output Voltage High

Positive Supply Voltage

(Note 9)

1.3 2.0

0.9 1.5

µA210

UNITSMIN TYP MAXSYMBOLPARAMETER

I

SINK

= 5mA V0.4V

OL

Output Voltage Low

CS = 3V

µA±10I

L

Three-State Leakage Current

CS = 3V

pF15C

OUT

Three-State Output

Capacitance

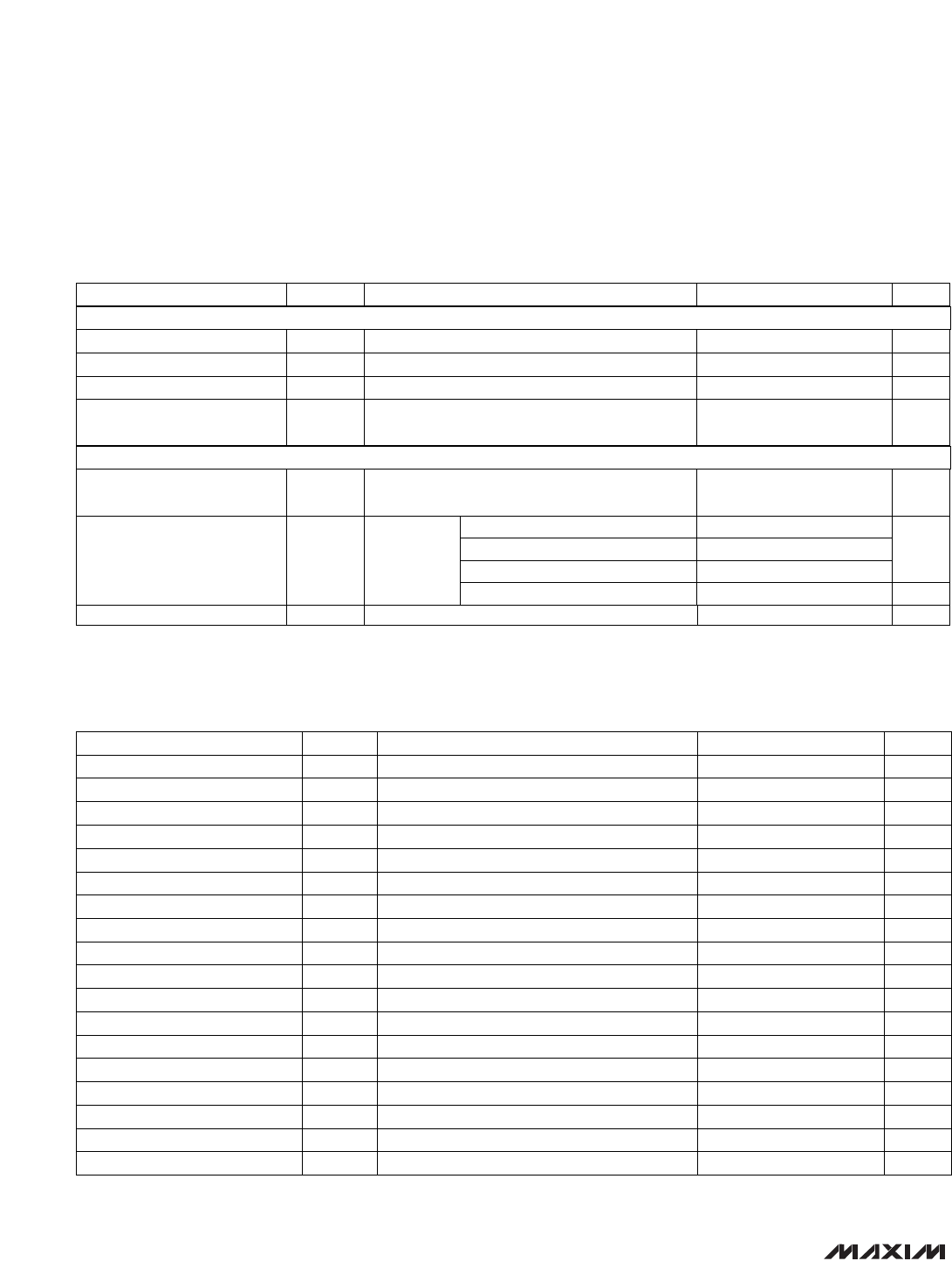

ELECTRICAL CHARACTERISTICS—MAX1281 (continued)

(V

DD1

= V

DD2

= +2.7V to +3.6V, COM = GND, f

SCLK

= 4.8MHz, 50% duty cycle, 16 clocks/conversion cycle (300ksps), external

+2.5V at REF, REFADJ = V

DD1

, T

A

= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at T

A

= +25°C.)

TIMING CHARACTERISTICS—MAX1280

(Figures 1, 2, 6, 7; V

DD1

= V

DD2

= +4.5V to +5.5V; T

A

= T

MIN

to T

MAX

; unless otherwise noted.)

C

LOAD

= 20pF

C

LOAD

= 20pF

C

LOAD

= 20pF

C

LOAD

= 20pF

C

LOAD

= 20pF

C

LOAD

= 20pF

C

LOAD

= 20pF

C

LOAD

= 20pF

CONDITIONS

ns

100

t

CSW

CS Pulse Width High

ns

65

t

STE

CS Fall to SSTRB Enable

ns

65

t

DOE

CS Fall to DOUT Enable

ns

10 65

t

STD

CS Rise to SSTRB Disable

ns

10 65

t

DOD

CS Rise to DOUT Disable

ns

80

t

STV

SCLK Rise to SSTRB Valid

ns

80

t

DOV

SCLK Rise to DOUT Valid

ns

62

t

CL

SCLK Pulse Width Low

ns

62

t

CH

ns

156

t

CP

SCLK Period

SCLK Pulse Width High

ns

10 20

t

STH

SCLK Rise to SSTRB Hold

ns

10 20

t

DOH

SCLK Rise to DOUT Hold

ns

35

t

CS1

CS Rise to SCLK Rise Ignore

ns

35

t

CSO

SCLK Rise to CS Fall Ignore

ns

35

t

DS

DIN to SCLK Setup

ns

0

t

DH

DIN to SCLK Hold

ns

35

t

CSS

CS Fall to SCLK Rise Setup

ns

0

t

CSH

SCLK Rise to CS Rise Hold

UNITSMIN TYP MAXSYMBOLPARAMETER

Operating mode

Reduced-power mode (Note 11)

Fast power-down (Note 11)

Full power-down (Note 11)

V

DD1

= V

DD2

= 2.7V to 3.6V, midscale input mV±0.5 ±2.0PSRPower-Supply Rejection

DIGITAL OUTPUTS (DOUT, SSTRB)

POWER SUPPLY