Datasheet

DS2155

208 of 238

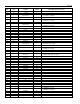

35. FUNCTIONAL TIMING DIAGRAMS

35.1 T1 Mode

Figure 35-1. Receive-Side D4 Timing

Note 1: RSYNC in the frame mode (IOCR1.5 = 0) and double-wide frame sync is not enabled (IOCR1.6 = 0).

Note 2: RSYNC in the frame mode (IOCR1.5 = 0) and double-wide frame sync is enabled (IOCR1.6 = 1).

Note 3: RSYNC in the multiframe mode (IOCR1.5 = 1).

Note 4: RLINK data (Fs bits) is updated one bit prior to even frames and held for two frames.

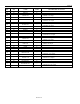

Figure 35-2. Receive-Side ESF Timing

Note 1: RSYNC in frame mode (IOCR1.4 = 0) and double-wide frame sync is not enabled (IOCR1.6 = 0).

Note 2: RSYNC in frame mode (IOCR1.4 = 0) and double-wide frame sync is enabled (IOCR1.6 = 1).

Note 3: RSYNC in multiframe mode (IOCR1.4 = 1).

Note 4: ZBTSI mode disabled (T1RCR2.2 = 0).

Note 5: RLINK data (FDL bits) is updated one bit time before odd frames and held for two frames.

Note 6: ZBTSI mode is enabled (T1RCR2.2 = 1).

Note 7: RLINK data (Z bits) is updated one bit time before odd frames and held for four frames.

FRAME#

1

2345678910111212345

4

RLINK

RLCLK

3

RSYNC

1

RSYNC

RFSYNC

2

RSYNC

123456789101112

1

2

3

6

RFSYNC

FRAME#

TLCLK

RSYNC

RSYNC

RSYNC

TLINK

13141516171819202122232412345

4

RLCLK

RLINK

5

7