User guide

Table Of Contents

- Return to Menu

- System Generator for DSP

- Table of Contents

- About This Guide

- Introduction

- Installation

- Release Information

- Getting Started

- Introduction

- Lesson 1 - Design Creation Basics

- The System Generator Design Flow

- The Xilinx DSP Blockset

- Defining the FPGA Boundary

- Adding the System Generator Token

- Creating the DSP Design

- Generating the HDL Code

- Model-Based Design using System Generator

- Creating Input Vectors using MATLAB

- Lesson 1 Summary

- Lab Exercise: Using Simulink

- Lab Exercise: Getting Started with System Generator

- Lesson 2 - Fixed Point and Bit Operations

- Lesson 3 - System Control

- Lesson 4 - Multi-Rate Systems

- Lesson 5 - Using Memories

- Lesson 6 - Designing Filters

- Additional Examples and Tutorials

- Index

System Generator for DSP Getting Started Guide www.xilinx.com 9

UG639 (v 12.2) July 23, 2010

Conventions

Online Document

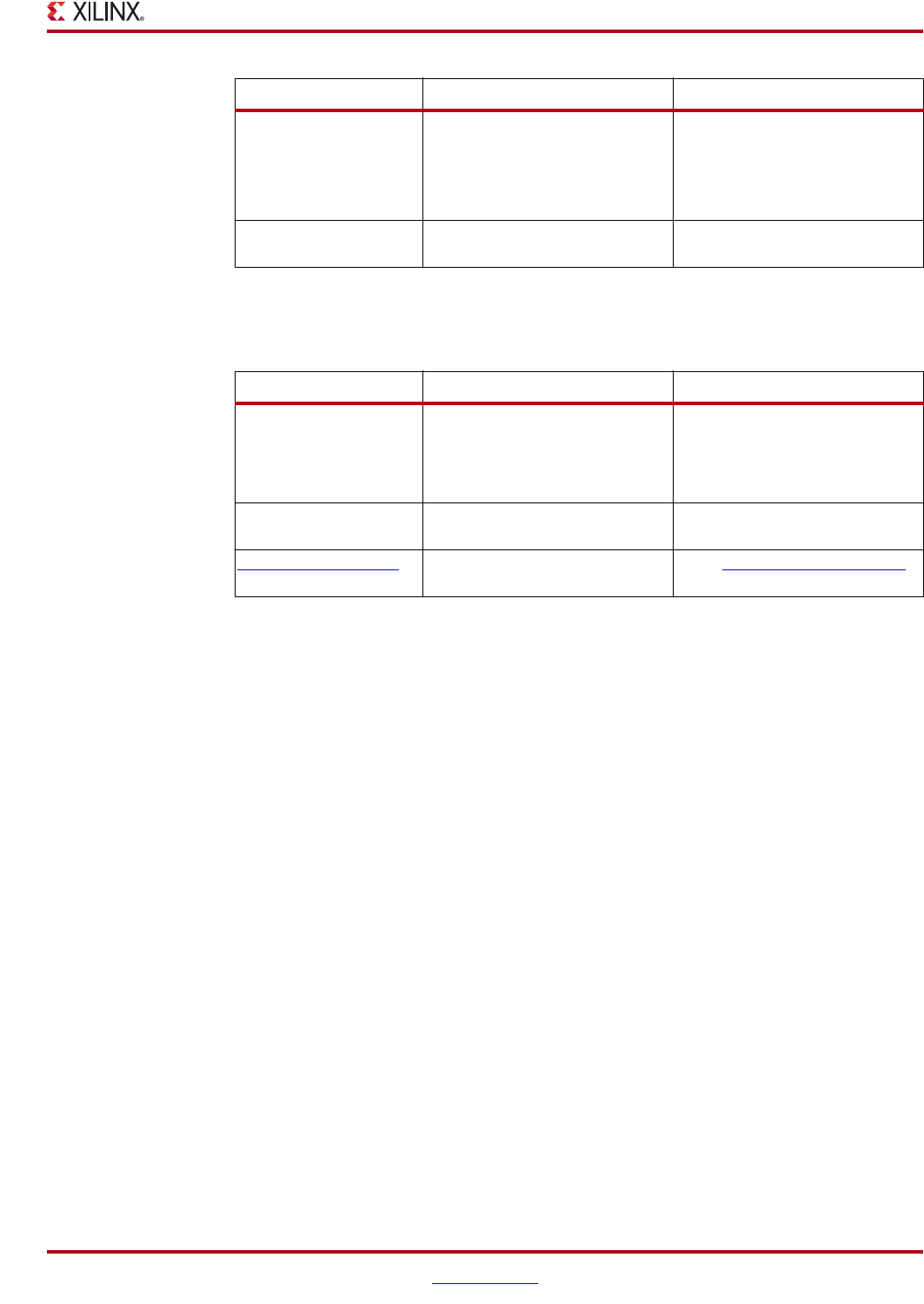

The following conventions are used in this document:

Vertical ellipsis

.

.

.

Repetitive material that has

been omitted

IOB #1: Name = QOUT’

IOB #2: Name = CLKIN’

.

.

.

Horizontal ellipsis . . . Repetitive material that has

been omitted

allow block block_name loc1

loc2 ... locn;

Convention Meaning or Use Example

Convention Meaning or Use Example

Blue text Cross-reference link to a

location in the current

document

See the topic “Additional

Resources” for details.

Refer to “Title Formats” in

Chapter 1 for details.

Red text Cross-reference link to a

location in another document

See Figure 2-5 in the Virtex-II

Platform FPGA User Guide.

Blue, underlined text

Hyperlink to a website (URL) Go to http://www.xilinx.com

for the latest speed files.