User guide

Table Of Contents

- Return to Menu

- System Generator for DSP

- Table of Contents

- About This Guide

- Introduction

- Installation

- Release Information

- Getting Started

- Introduction

- Lesson 1 - Design Creation Basics

- The System Generator Design Flow

- The Xilinx DSP Blockset

- Defining the FPGA Boundary

- Adding the System Generator Token

- Creating the DSP Design

- Generating the HDL Code

- Model-Based Design using System Generator

- Creating Input Vectors using MATLAB

- Lesson 1 Summary

- Lab Exercise: Using Simulink

- Lab Exercise: Getting Started with System Generator

- Lesson 2 - Fixed Point and Bit Operations

- Lesson 3 - System Control

- Lesson 4 - Multi-Rate Systems

- Lesson 5 - Using Memories

- Lesson 6 - Designing Filters

- Additional Examples and Tutorials

- Index

System Generator for DSP Getting Started Guide www.xilinx.com 83

UG639 (v 12.2) July 23, 2010

Lesson 5 - Using Memories

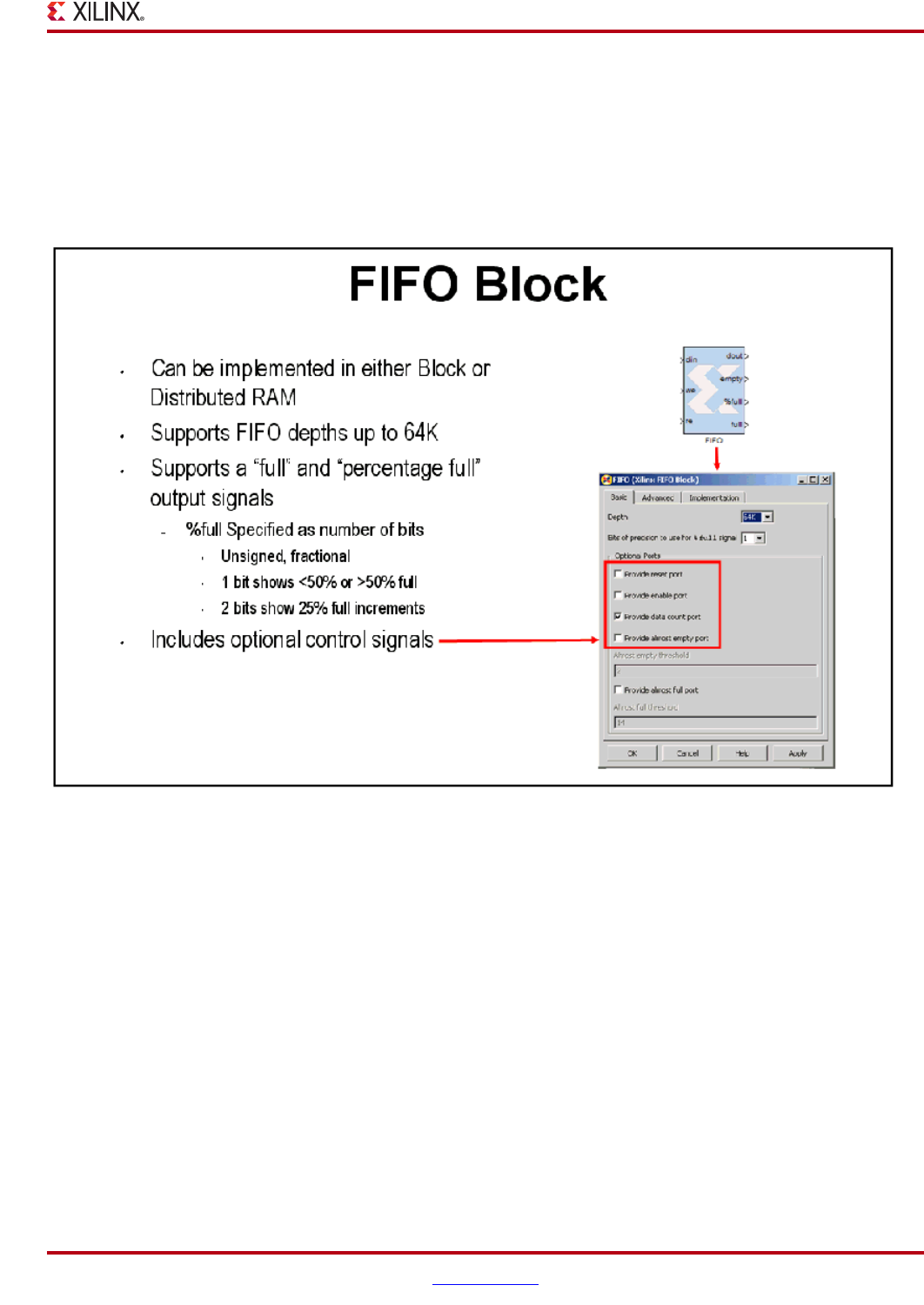

The FIFO Block

The FIFO block supports both Block RAM and Distributed RAM implementations. Depths up to 64K are supported.

Three output flags are supported, empty, full and %full. The %full flag is set depending on a bit width

specification. One bit will be zero until the FIFO is 50% full, then it will set to.5. Two bits will be zero until 20% full,

then .25, .5 and .75.