User guide

Table Of Contents

- Return to Menu

- System Generator for DSP

- Table of Contents

- About This Guide

- Introduction

- Installation

- Release Information

- Getting Started

- Introduction

- Lesson 1 - Design Creation Basics

- The System Generator Design Flow

- The Xilinx DSP Blockset

- Defining the FPGA Boundary

- Adding the System Generator Token

- Creating the DSP Design

- Generating the HDL Code

- Model-Based Design using System Generator

- Creating Input Vectors using MATLAB

- Lesson 1 Summary

- Lab Exercise: Using Simulink

- Lab Exercise: Getting Started with System Generator

- Lesson 2 - Fixed Point and Bit Operations

- Lesson 3 - System Control

- Lesson 4 - Multi-Rate Systems

- Lesson 5 - Using Memories

- Lesson 6 - Designing Filters

- Additional Examples and Tutorials

- Index

8 www.xilinx.com System Generator for DSP Getting Started Guide

UG639 (v 12.2) July 23, 2010

Preface: About This Guide

Additional Resources

To find additional documentation, see the Xilinx website at:

http://www.xilinx.com/support/documentation/index.htm

.

To search the Answer Database of silicon, software, and IP questions and answers, or to

create a technical support WebCase, see the Xilinx website at:

http://www.xilinx.com/support/mysupport.htm

.

Conventions

This document uses the following conventions. An example illustrates each convention.

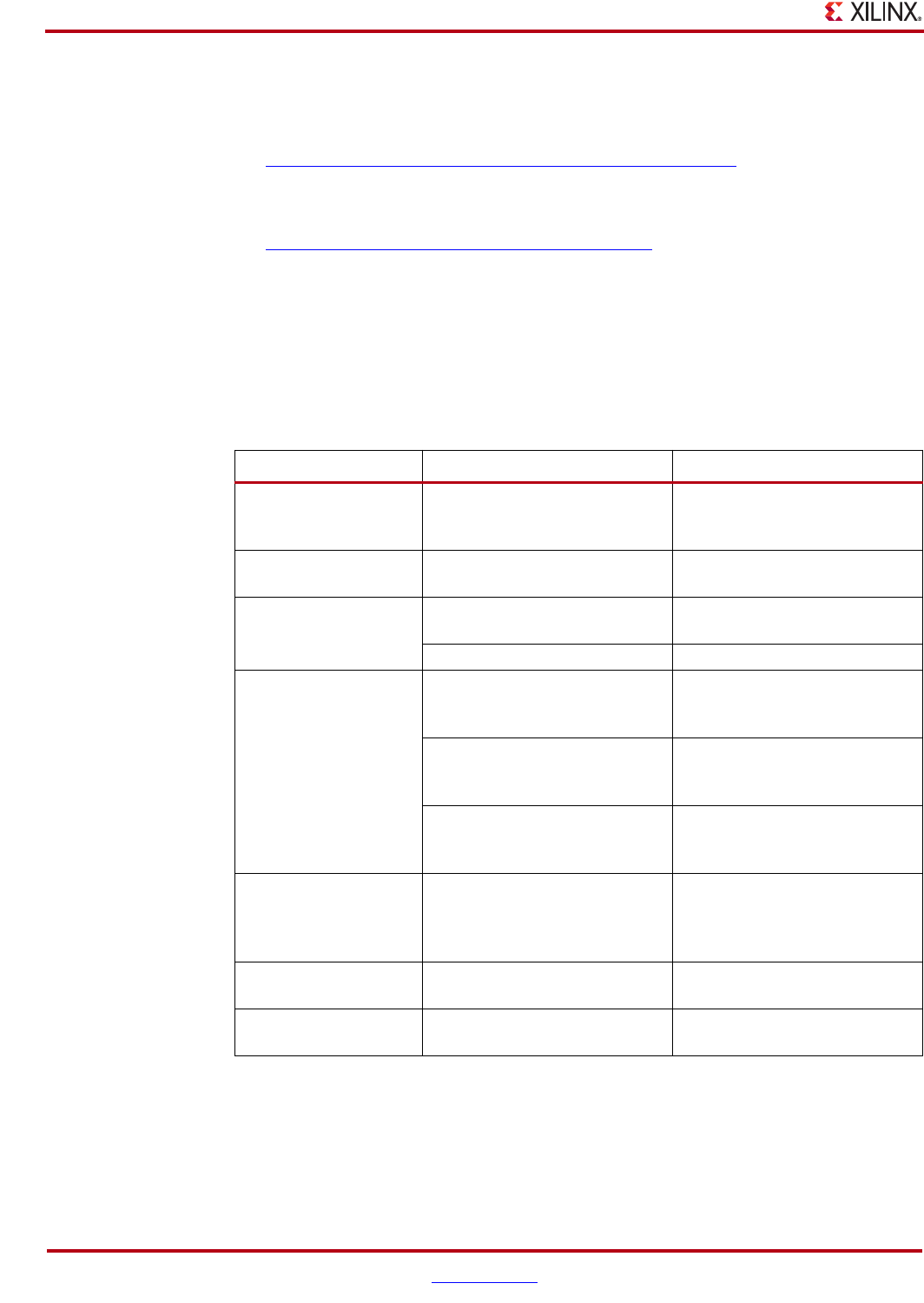

Typographical

The following typographical conventions are used in this document:

Convention Meaning or Use Example

Courier font Messages, prompts, and

program files that the system

displays

speed grade: - 100

Courier bold Literal commands that you

enter in a syntactical statement

ngdbuild design_name

Helvetica bold Commands that you select from

a menu

File → Open

Keyboard shortcuts Ctrl+C

Italic font Variables in a syntax statement

for which you must supply

values

ngdbuild design_name

References to other manuals See the Development System

Reference Guide for more

information.

Emphasis in text If a wire is drawn so that it

overlaps the pin of a symbol,

the two nets are not connected.

Square brackets [ ] An optional entry or parameter.

However, in bus specifications,

such as bus[7:0], they are

required.

ngdbuild [option_name]

design_name

Braces { } A list of items from which you

must choose one or more

lowpwr ={on|off}

Vertical bar | Separates items in a list of

choices

lowpwr ={on|off}