User guide

Table Of Contents

- Return to Menu

- System Generator for DSP

- Table of Contents

- About This Guide

- Introduction

- Installation

- Release Information

- Getting Started

- Introduction

- Lesson 1 - Design Creation Basics

- The System Generator Design Flow

- The Xilinx DSP Blockset

- Defining the FPGA Boundary

- Adding the System Generator Token

- Creating the DSP Design

- Generating the HDL Code

- Model-Based Design using System Generator

- Creating Input Vectors using MATLAB

- Lesson 1 Summary

- Lab Exercise: Using Simulink

- Lab Exercise: Getting Started with System Generator

- Lesson 2 - Fixed Point and Bit Operations

- Lesson 3 - System Control

- Lesson 4 - Multi-Rate Systems

- Lesson 5 - Using Memories

- Lesson 6 - Designing Filters

- Additional Examples and Tutorials

- Index

72 www.xilinx.com System Generator for DSP Getting Started Guide

UG639 (v 12.2) July 23, 2010

Chapter 4: Getting Started

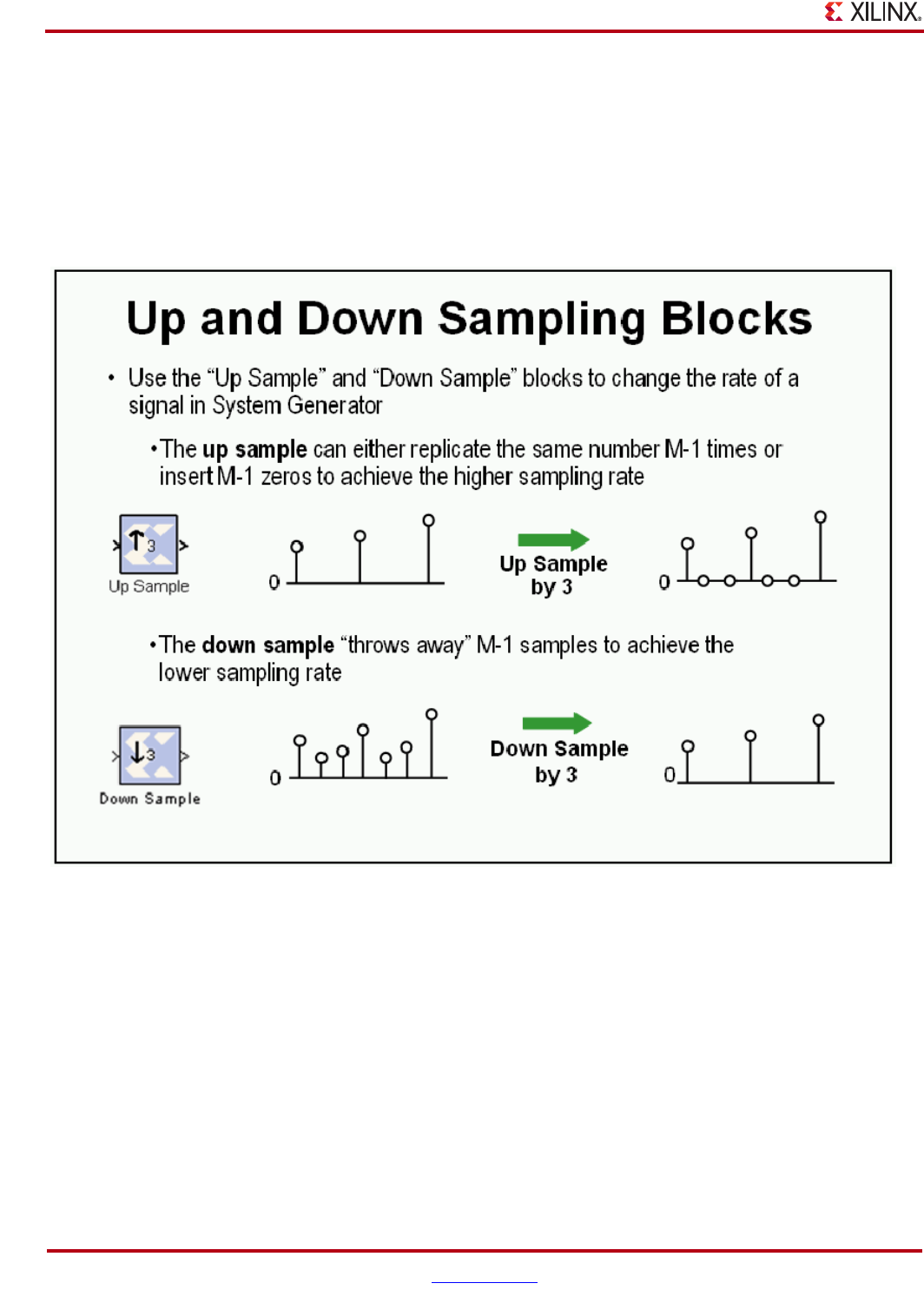

Up and Down Sampling Blocks

System Generator includes Up Sample and Down Sample blocks that change the system sample rate. The Up

Sample block adds additional samples to the signal to achieve the desired rate change. The value of these new

samples is either zero or the value of the last actual sample depending on the block options. The Down Sample

block simply discards samples until it achieves the desired rate change. For example, downsample by 3 means to

discard 2 out of every 3 samples.