User guide

Table Of Contents

- Return to Menu

- System Generator for DSP

- Table of Contents

- About This Guide

- Introduction

- Installation

- Release Information

- Getting Started

- Introduction

- Lesson 1 - Design Creation Basics

- The System Generator Design Flow

- The Xilinx DSP Blockset

- Defining the FPGA Boundary

- Adding the System Generator Token

- Creating the DSP Design

- Generating the HDL Code

- Model-Based Design using System Generator

- Creating Input Vectors using MATLAB

- Lesson 1 Summary

- Lab Exercise: Using Simulink

- Lab Exercise: Getting Started with System Generator

- Lesson 2 - Fixed Point and Bit Operations

- Lesson 3 - System Control

- Lesson 4 - Multi-Rate Systems

- Lesson 5 - Using Memories

- Lesson 6 - Designing Filters

- Additional Examples and Tutorials

- Index

System Generator for DSP Getting Started Guide www.xilinx.com 55

UG639 (v 12.2) July 23, 2010

Lesson 2 - Fixed Point and Bit Operations

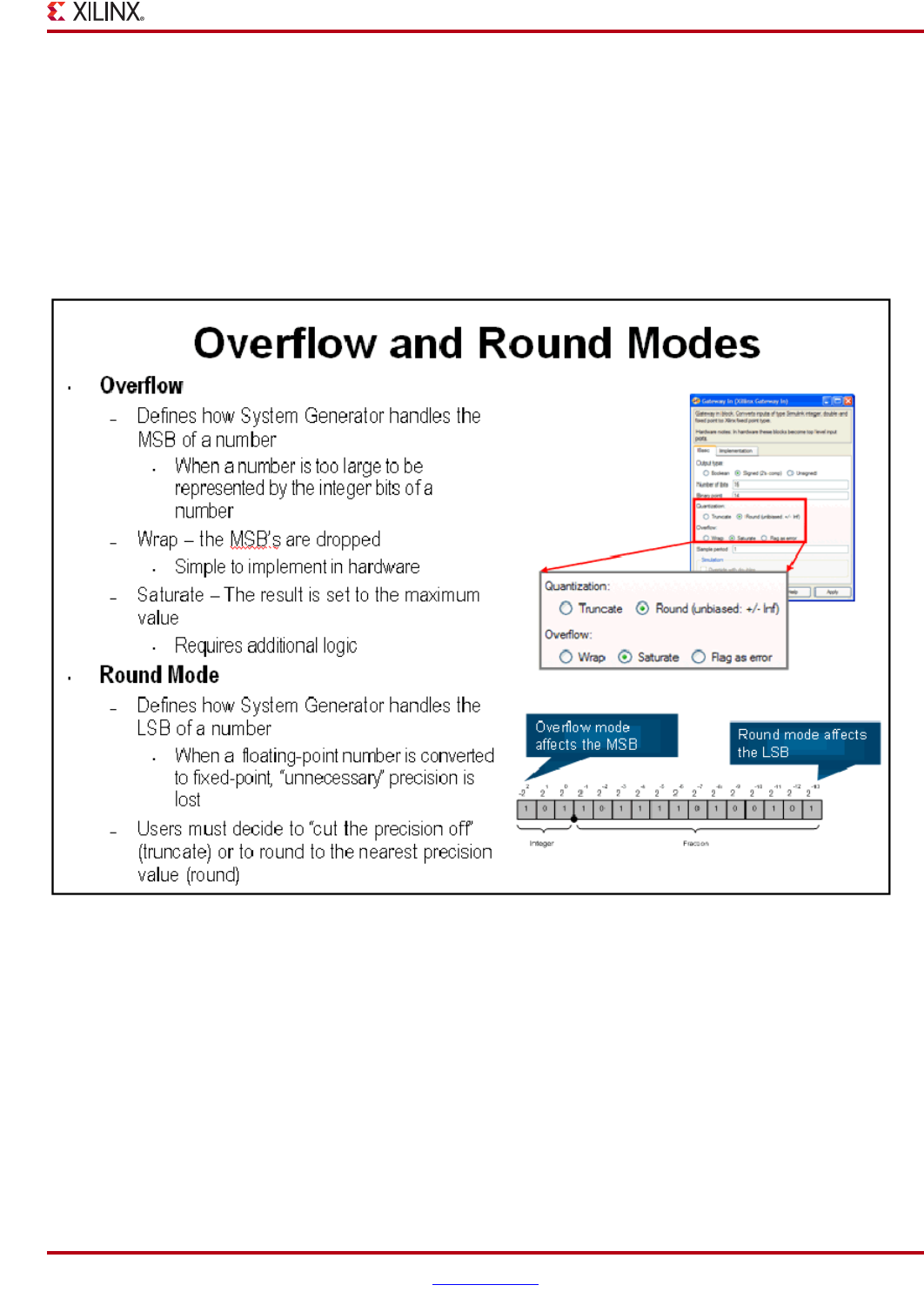

Overflow and Round Modes

System Generator supports the overflow modes Wrap, Saturate and Flag as error. Wrap is the default because it has

the least cost in hardware. Saturate requires System Generator to insert logic to perform that operation and

therefore should only be used when necessary for the application

System Generator supports Truncate and Round of the LSB during the quantization process. Similar to the Wrap

mode for overflow mode, Truncat e has minimal hardware cost and is the default. Specifying the Round mode

requires System Generator to insert extra logic and should be used when only necessary for the application.