User guide

Table Of Contents

- Return to Menu

- System Generator for DSP

- Table of Contents

- About This Guide

- Introduction

- Installation

- Release Information

- Getting Started

- Introduction

- Lesson 1 - Design Creation Basics

- The System Generator Design Flow

- The Xilinx DSP Blockset

- Defining the FPGA Boundary

- Adding the System Generator Token

- Creating the DSP Design

- Generating the HDL Code

- Model-Based Design using System Generator

- Creating Input Vectors using MATLAB

- Lesson 1 Summary

- Lab Exercise: Using Simulink

- Lab Exercise: Getting Started with System Generator

- Lesson 2 - Fixed Point and Bit Operations

- Lesson 3 - System Control

- Lesson 4 - Multi-Rate Systems

- Lesson 5 - Using Memories

- Lesson 6 - Designing Filters

- Additional Examples and Tutorials

- Index

System Generator for DSP Getting Started Guide www.xilinx.com 13

UG639 (v 12.2) July 23, 2010

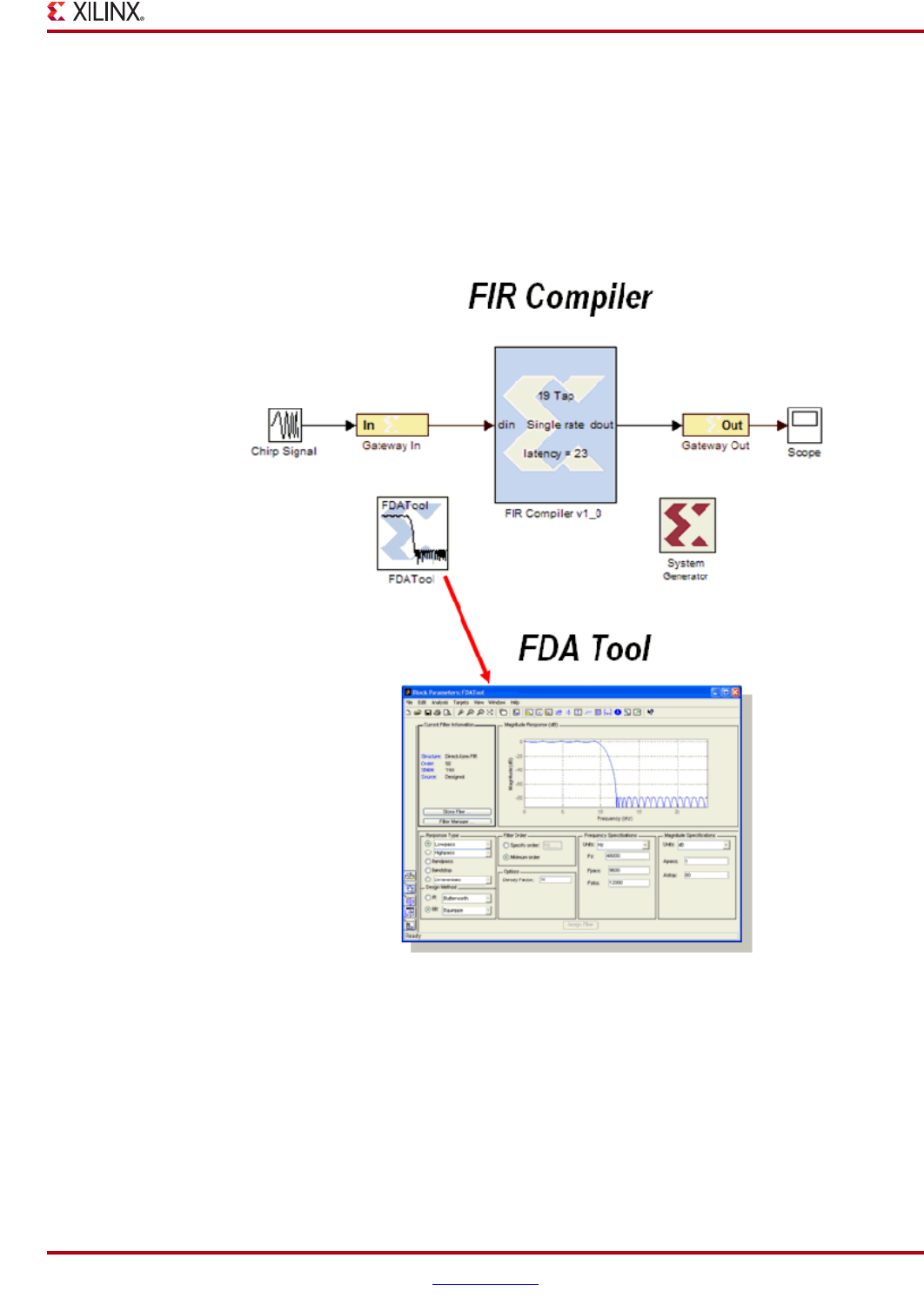

FIR Filter Generation

FIR Filter Generation

System Generator includes a FIR Compiler block that targets the dedicated DSP48

hardware resources in the Virtex®-4 and Virtex-5 devices to create highly optimized

implementations that can run in excess of 500 Mhz. Configuration options allow

generation of direct, polyphase decimation, polyphase interpolation and oversampled

implementations. Standard MATLAB functions such as fir2 or the MathWorks FDAtool

can be used to create coefficients for the Xilinx FIR Compiler.