User`s guide

Table Of Contents

- Preface

- Quick Start

- LTI Models

- Introduction

- Creating LTI Models

- LTI Properties

- Model Conversion

- Time Delays

- Simulink Block for LTI Systems

- References

- Operations on LTI Models

- Arrays of LTI Models

- Model Analysis Tools

- The LTI Viewer

- Introduction

- Getting Started Using the LTI Viewer: An Example

- The LTI Viewer Menus

- The Right-Click Menus

- The LTI Viewer Tools Menu

- Simulink LTI Viewer

- Control Design Tools

- The Root Locus Design GUI

- Introduction

- A Servomechanism Example

- Controller Design Using the Root Locus Design GUI

- Additional Root Locus Design GUI Features

- References

- Design Case Studies

- Reliable Computations

- Reference

- Category Tables

- acker

- append

- augstate

- balreal

- bode

- c2d

- canon

- care

- chgunits

- connect

- covar

- ctrb

- ctrbf

- d2c

- d2d

- damp

- dare

- dcgain

- delay2z

- dlqr

- dlyap

- drmodel, drss

- dsort

- dss

- dssdata

- esort

- estim

- evalfr

- feedback

- filt

- frd

- frdata

- freqresp

- gensig

- get

- gram

- hasdelay

- impulse

- initial

- inv

- isct, isdt

- isempty

- isproper

- issiso

- kalman

- kalmd

- lft

- lqgreg

- lqr

- lqrd

- lqry

- lsim

- ltiview

- lyap

- margin

- minreal

- modred

- ndims

- ngrid

- nichols

- norm

- nyquist

- obsv

- obsvf

- ord2

- pade

- parallel

- place

- pole

- pzmap

- reg

- reshape

- rlocfind

- rlocus

- rltool

- rmodel, rss

- series

- set

- sgrid

- sigma

- size

- sminreal

- ss

- ss2ss

- ssbal

- ssdata

- stack

- step

- tf

- tfdata

- totaldelay

- zero

- zgrid

- zpk

- zpkdata

- Index

parallel

11-169

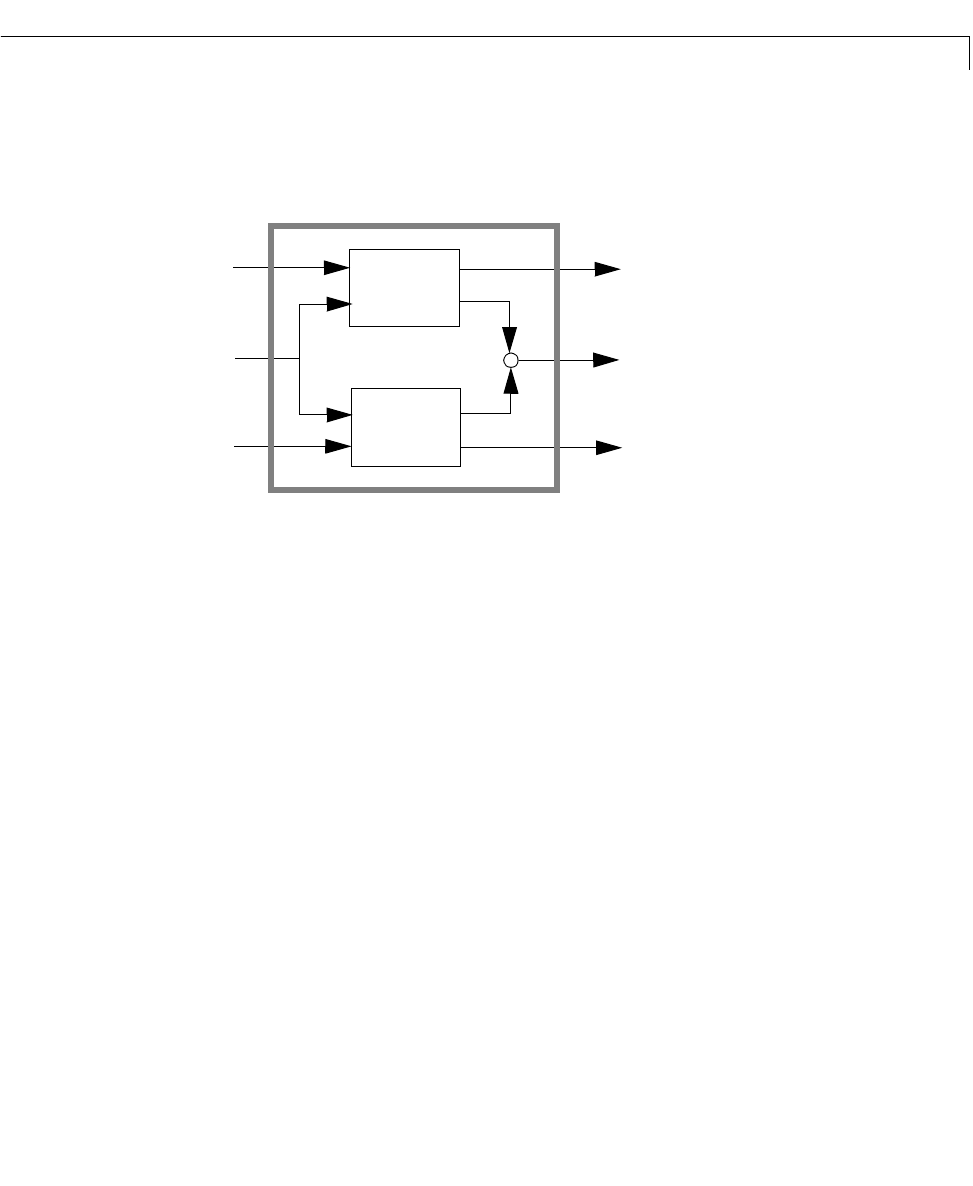

sys = parallel(sys1,sys2,inp1,inp2,out1,out2) forms the more general

parallel connection.

The index vectors

inp1 and inp2 s pecify which inputs of sys1 and which

inputs of

sys2 are connect ed. Similarly, the index vectors out1 and out2

specify which outputs of sys1 and which outputs of sys2 are summed.

The resulting model

sys has as inputs and as

outputs.

Example See “Steady-State Design” on page 9-51 for an example.

See Also append Append LTI systems

feedback Feedback connecti on

series Series connection

sys1

sys2

+

+

sys

u

u

2

u

1

y

2

y

1

y

z

1

v

1

z

2

v

2

u

1

u

2

y

1

y

2

v

1

uv

2

;;[]

z

1

yz

2

;;[]