User Manual

D03Rev2.3

8

DMT proprietary & confidential: product information is subject to change without notice.

Domintech Co., Ltd. Tel: +886-2-2290-1288 Fax: +886-2-2290-1266 http://www.domintech.com.tw

enabled. When the freefall interrupt is enabled, DMARD03 will watch closely the acceleration values of

all three axes as compared to some threshold. The INTx pin will directly reflect the comparison result,

in other words the result is not latched. The INTx pin will be logic-1 if all three acceleration magnitudes

are below the designated threshold value, which potentially indicates a freefall in process. On the other

hand, the INTx pin will be logic-0 if any of three acceleration magnitudes rises above the threshold.

The freefall interrupt flag (FFInt, 0Ch:bit7) serves the same purpose and manner as the INTx pin. This

flag can be read via the SPI/I2C digital interface, and therefore is an alternative to the INTx pin if end

users have GPIO constraint. See "Interrupt Status Registers" for details. User can set freefall threshold,

see "Freefall Threshold" for details.

High-G Latch Control

HGL (08h:bit3) is the high-G latch control. Under some circumstances the high-G detection event

may need to be latched. Logic-1 HGL will cause the high-G detection results latched. See “High-G

Detection” for details on high-G detection.

Bandwidth

Tms (08h:bit2) is used to setup the internal ADC sampling period, together with N[1:0] (08h:bit1,

0), which is to setup the digital filtering of ADC output data, to obtain the desired bandwidth. Digital

filters can be selectively activated to reduce the bandwidth to as low as 20 Hz. A moving average filter

of various lengths is implemented as the digital filter. Please see Table 6 for the sampling period and

frequency settable by Tms, and Table 7 for the moving average length settable by N[1:0]. Bandwidth

table can be found in Table 8.

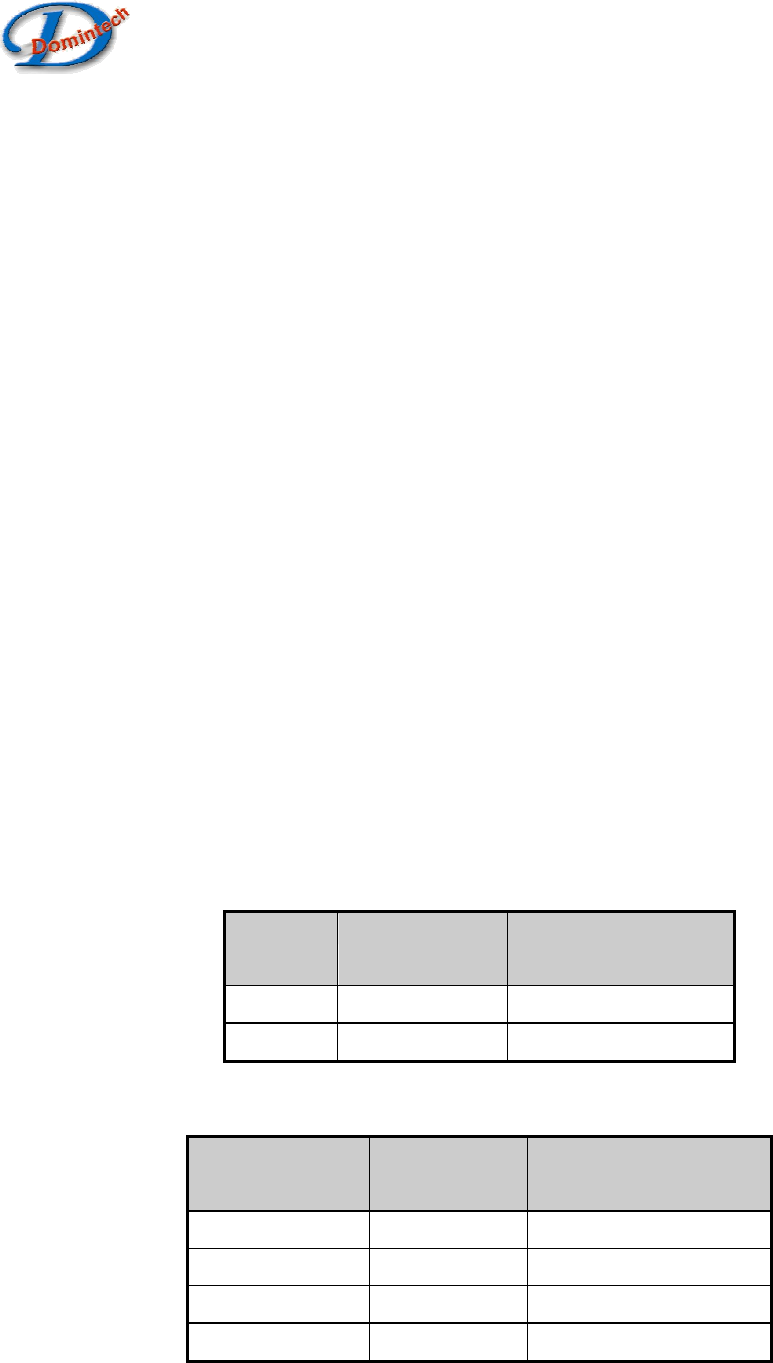

Table 6: Sampling Period Table

Tms

(08h: bit2)

Sampling Period

(ms)

Sampling Frequency

(Hz)

0

2.925 342

1

1.462 684

Table 7: Moving Average Length Table

N[1]

(08h: bit1)

N[0]

(08h: bit0)

Average Order

0 0

8

0 1

4

1 0

2

1 1

1