User manual

Table Of Contents

- Adaptive Services II PIC

- Adaptive Services II FIPS PIC

- ATM2 DS3 IQ PIC

- ATM2 E3 IQ PIC

- ATM2 OC3/STM1 IQ PIC

- ATM2 OC12/STM4 IQ PIC

- Channelized DS3 IQ PIC

- Channelized E1 IQ PIC

- Channelized OC12 PIC

- Channelized OC12 IQ PIC

- Channelized OC3 IQ PIC

- Channelized STM1 IQ PIC

- Channelized T1 IQ PIC

- DS3 PIC

- E1 PIC

- E3 PIC

- E3 IQ PIC

- EIA-530 PIC

- ES PIC

- Fast Ethernet PICs

- Gigabit Ethernet PIC with SFP

- Gigabit Ethernet IQ PIC with SFP

- Gigabit Ethernet IQ2 PIC with SFP

- Link Services PIC

- MultiServices 100 PIC

- SONET/SDH OC3c/STM1 PIC

- SONET/SDH OC3c/STM1 PIC with SFP

- SONET/SDH OC3/STM1 (Multi-Rate) PIC with SFP

- SONET/SDH OC12c/STM4 PIC

- SONET/SDH OC12/STM4 (Multi-Rate) PIC with SFP

- SONET/SDH OC48c/STM16 PIC with SFP

- T1 PIC

- Tunnel Services PIC

- High Availability Features

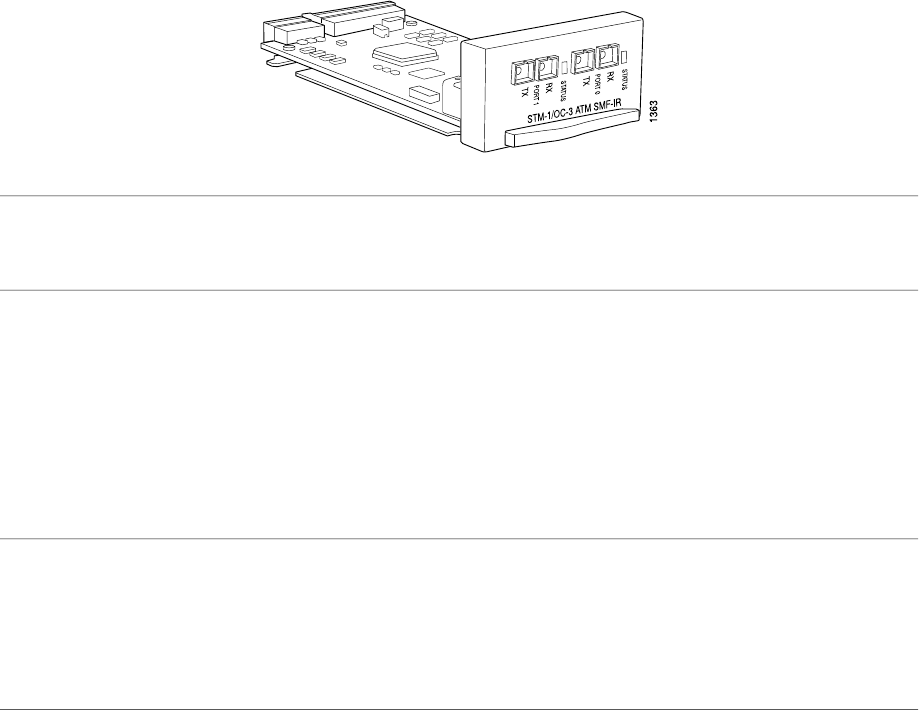

ATM2 OC3/STM1 IQ PIC

■

JUNOS 6.1 and laterSoftware release

■

Two OC3 ports

■

Power requirement: 0.41 A @ 48 V (20 W)

■

Intelligent queuing (IQ) PICs support fine-grained queuing per logical interface

■

Conforms to ANSI T1.105-1991 and T1E1.2/93-020R1

■

ATM and SONET/SDH standards compliant

■

Alarm and event counting and detection

■

Compatible with well-known ATM switches

■

ATM switch ID, which displays the switch IP address and local interface name of the

adjacent Fore ATM switches

Description

■

Single 3010 SAR for segmentation and reassembly into 53 byte ATM cells

■

High-performance parsing of SONET/SDH frames

■

ASIC-based packet segmentation and reassembly (SAR) management and output port

queuing

■

64 MB SDRAM memory for ATM SAR

■

Packet buffering, Layer 2 parsing

Hardware features

ATM2 OC3/STM1 IQ PIC ■ 13

ATM2 OC3/STM1 IQ PIC