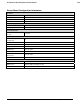

Workstation Test Submission (WTS) Report

Errata and Contingencies Intel® Workstation Board WX58BP

10 April 10, 2009

Errata and Contingencies

Operating System Failing Test

Expiry date

ID Number Type Error Description

Windows Vista

Windows Vista 64-bit

PCI Hardware

Compliance

Test For

Systems

Running

Windows Vista

(PCIHCT)

12/31/2009 1098

Erratum

Bit range 15:0 (Extended Capability ID)in the Enhanced

Capability Header register (offset 0h) in the Unrecognized

Enhanced Capability ID 13 table is Dh. It must be in the

range [0x0 - 0xB] as all other Capability IDs are reserved.

Windows Vista

Windows Vista 64-bit

PCI Hardware

Compliance

Test For

Systems

Running

Windows Vista

(PCIHCT)

12/31/2009 1150

Erratum

Assertion 3CDD17AF-215E-4921-894F-C99434A3B3CA Bit

range 31:21 (Reserved_3)in the Uncorrectable Error Mask

register (offset 8h) in the Advanced Error Reporting

Capability table must be read-only and always return 0 .

Assertion FF8BC1A1-79B5-480A-9439-BF81AEDF4183 Bit

13 (Flow Control Protocol Error Severity) in the

Uncorrectable Error Severity register (offset Ch) in the

Advanced Error Reporting Capability table must be read-

only and always return 1 . It was found to return 0.

Assertion 461CA4DE-9266-4420-9B5F-F33622A5D02B Bit

range 31:21 (Reserved_3)in the Uncorrectable Error

Severity register (offset Ch) in the Advanced Error

Reporting Capability table must be read-only and always

return 0 .

Windows Vista

Windows Vista 64-bit

PCI Hardware

Compliance

Test For

Systems

Running

Windows Vista

(PCIHCT)

12/31/2009 385

Erratum

The following PCI Compliance test failure is acceptable:

Bit 15 (Bridge Configuration Retry Enable) in the Device

Control register (offset 8h) in the PCI Express Capability

table must be read-only and always return 0 as it is

reserved for devices other than PCI Express to PCI/PCI-X

Bridges.

Assertion 13A41D3E-2576-41DC-A67C-525DA3637CEA

This failure is acceptable because this is a PCIe 1.1

feature and the WLP requires compliance with only PCIe

1.0a.

Windows Vista

Windows Vista 64-bit

PCI Hardware

Compliance

Test For

Systems

Running

Windows Vista

(PCIHCT)

12/31/2009 1114

Erratum

Bit range 9:4 (Negotiated Link Width)in the Link Status

register (offset 12h) in the PCI Express Capability table is

0h. It must be in the set of values {0x1, 0x2, 0x4, 0x8,

0xc, 0x10, 0x20}.

Windows Vista

Windows Vista 64-bit

PCI Hardware

Compliance

Test For

Systems

Running

Windows Vista

(PCIHCT)

12/31/2009 474

Erratum

According to the PCI Express Base Specification, Rev 2.0

Section 7.8.8, this bit field is undefined when the link is

not up. If there is not PCIe device behind the bridge,

then the link can NOT be up and therefore the field is

undefined. Bit 13 in the same register (Link Status) can

be used to determine if the link is active (up). The

PCIHCT uses the Presence Detect State bit of the Slot

Status register to determine whether a child device is

present. However, the Presence Detect State bit only

returns valid data if the Slot Implemented bit is set (bit 8

of PCIe capabilities register). If the PCIe root port or

downstream port will never have a device behind it, the

Slot Implemented bit is cleared to 0. Per the spec, PDS

will always be 1 when the Slot Implemented bit is clear.

Therefore PDS can not be used to determine device

presence when the SI bit is clear.