Intel Core Duo Processor and Intel Core Solo Processor on 65 nm Process

Datasheet 21

Electrical Specifications

3 Electrical Specifications

3.1 Power and Ground Pins

For clean, on-chip power distribution, the processor will have a large number of V

CC

(power) and V

SS

(ground) inputs. All power pins must be connected to V

CC

power

planes while all V

SS

pins must be connected to system ground planes. Use of multiple

power and ground planes is recommended to reduce I*R drop. Please contact your

Intel representative for more details. The processor V

CC

pins must be supplied the

voltage determined by the VID (Voltage ID) pins.

3.2 FSB Clock (BCLK[1:0]) and Processor Clocking

BCLK[1:0] directly controls the FSB interface speed as well as the core frequency of the

processor. As in previous generation processors, the Intel Core Duo processor and Intel

Core Solo processors’ core frequency is a multiple of the BCLK[1:0] frequency. The

processor uses a differential clocking implementation.

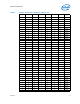

3.3 Voltage Identification

The processor uses seven voltage identification pins, VID[6:0], to support automatic

selection of power supply voltages. The VID pins for the processor are CMOS outputs

driven by the processor VID circuitry. Table 2 specifies the voltage level corresponding

to the state of VID[6:0]. A 1 in this refers to a high-voltage level and a 0 refers to low-

voltage level.

Table 2. Voltage Identification Definition (Sheet 1 of 4)

VID6 VID5 VID4 VID3 VID2 VID1 VID0 V

CC

(V)

00000001.5000

00000011.4875

00000101.4750

00000111.4625

00001001.4500

00001011.4375

00001101.4250

00001111.4125

00010001.4000

00010011.3875

00010101.3750

00010111.3625

00011001.3500

00011011.3375

00011101.3250

00011111.3125