Technical Product Specification

Table Of Contents

- 1. Introduction

- 2. Product Overview

- 3. Functional Architecture

- 3.1 Processor Support

- 3.1.1 Processor Population Rules

- 3.1.2 Multiple Processor Initialization

- 3.1.3 Enhanced Intel SpeedStep® Technology

- 3.1.4 Intel® Extended Memory 64 Technology (Intel® EM64T)

- 3.1.5 Execute Disable Bit Feature

- 3.1.6 Multi-Core Processor Support

- 3.1.7 Intel® Virtualization Technology

- 3.1.8 Platform Environmental Control Interface (PECI)

- 3.1.9 Common Enabling Kit (CEK) Design Support

- 3.2 Intel® 5400 Memory Controller Hub Chipset (Intel® 5400 MCH Chipset)

- 3.2.1 Processor Front-Side Buses

- 3.2.2 Snoop Filter

- 3.2.3 System Memory Controller and Memory Subsystem

- 3.2.3.1 Supported Memory

- 3.2.3.2 DIMM Population Rules and Supported DIMM Configurations

- 3.2.3.3 Minimum Memory Configuration

- 3.2.3.4 Memory upgrades

- 3.2.3.5 ECC Code Support

- 3.2.3.6 Memory Sparing

- 3.2.3.7 FBD Memory Thermal Management

- 3.2.3.8 BIOS Support of Memory Subsystem

- 3.2.3.9 Memory Error Handing

- 3.2.3.10 Memory Error Reporting

- 3.3 Intel® 6321ESB I/O Controller Hub

- 3.4 PCI Subsystem

- 3.4.1 Intel® 6321ESB I/O Controller Hub PCI32: 32-bit, 33-MHz PCI Bus Segment

- 3.4.2 Intel® 6321ESB I/O Controller Hub Port 1: x4 PCI Express* Bus Segment

- 3.4.3 Intel® 6321ESB I/O Controller Hub Port 2: x4 PCI Express* Bus Segment

- 3.4.4 MCH to Intel® 6321ESB I/O Controller Hub Chip-to-Chip Interface: Two x4 PCI Express* Bus Segments

- 3.4.5 MCH Ports 5-8: x16 Gen 2 PCI Express* Bus Segment

- 3.4.6 Scan Order

- 3.4.7 Resource Assignment

- 3.4.8 Automatic IRQ Assignment

- 3.4.9 Legacy Option ROM Support

- 3.4.10 EFI PCI APIs

- 3.4.11 Legacy PCI APIs

- 3.5 Video Support

- 3.6 Network Interface Controller (NIC)

- 3.7 Super I/O

- 3.1 Processor Support

- 4. Server Management

- 4.1 Intel® 6321ESB I/O Controller Hub Integrated Baseboard Management Controller (Integrated BMC) Feature Set

- 4.2 Advanced Configuration and Power Interface (ACPI)

- 4.3 System Initialization

- 4.4 Integrated Front Panel User Interface

- 4.5 Platform Control

- 4.6 Standard Fan Management

- 4.7 Private Management I2C Buses

- 4.8 Integrated BMC Messaging Interfaces

- 4.9 Event Filtering and Alerting

- 4.10 Watchdog Timer

- 4.11 System Event Log (SEL)

- 4.12 Sensor Data Record (SDR) Repository

- 4.13 Field Replaceable Unit (FRU) Inventory Device

- 4.14 Non-maskable Interrupt (NMI)

- 4.15 General Sensor Behavior

- 4.16 Processor Sensors

- 4.16.1 Processor Status Sensors

- 4.16.2 Processor VRD Over-temperature Sensor

- 4.16.3 ThermalTrip Monitoring

- 4.16.4 Internal Error (IERR) Monitoring

- 4.16.5 Dynamic Processor Voltage Monitoring

- 4.16.6 Processor Temperature Monitoring

- 4.16.7 Processor Thermal Control Monitoring (ProcHot)

- 4.16.8 CPU Population Error Sensor

- 4.17 Intel® Remote Management Module 2 (Intel RMM2) Support

- 5. System BIOS

- 5.1 BIOS Identification String

- 5.2 BIOS User Interface

- 5.2.1 Logo/Diagnostic Screen

- 5.2.2 BIOS Setup Utility

- 5.2.3 Server Platform Setup Utility Screens

- 5.2.3.1 Main Screen

- 5.2.3.2 Advanced Screen

- 5.2.3.3 Security Screen

- 5.2.3.4 Server Management Screen

- 5.2.3.5 Server Management System Information Screen

- 5.2.3.6 Boot Options Screen

- 5.2.3.7 Boot Manager Screen

- 5.2.3.8 Error Manager Screen

- 5.2.3.9 Exit Screen

- 5.3 Loading BIOS Defaults

- 5.4 Rolling BIOS

- 5.5 OEM Binary

- 6. Connector/Header Locations and Pin-outs

- 7. Jumper Block Settings

- 8. Intel® Light-Guided Diagnostics

- 9. Power and Environmental Specifications

- 9.1 Intel® Server Board S5400SF Design Specifications

- 9.2 Server Board Power Requirements

- 9.2.1 Processor Power Support

- 9.2.2 Power Supply DC Output Requirements

- 9.2.3 Power-on Loading

- 9.2.4 Grounding

- 9.2.5 Standby Outputs

- 9.2.6 Remote Sense

- 9.2.7 Voltage Regulation

- 9.2.8 Dynamic Loading

- 9.2.9 Capacitive Loading

- 9.2.10 Closed-Loop Stability

- 9.2.11 Common Mode Noise

- 9.2.12 Ripple/Noise

- 9.2.13 Soft Starting

- 9.2.14 Timing Requirements

- 9.2.15 Residual Voltage Immunity in Standby Mode

- 10. Regulatory and Certification Information

- Appendix A: Integration and Usage Tips

- Appendix B: POST Code Diagnostic LED Decoder

- Appendix C: POST Error Messages and Handling

- Appendix D: EFI Shell Commands

- Appendix E: Supported Intel® Server Chassis

- Appendix F: 1U PCI Express* Gen 2 Riser Card

- Glossary

- Reference Documents

Intel

®

Server Board S5400SF TPS Functional Architecture

Revision 2.02

Intel order number: D92944-007

25

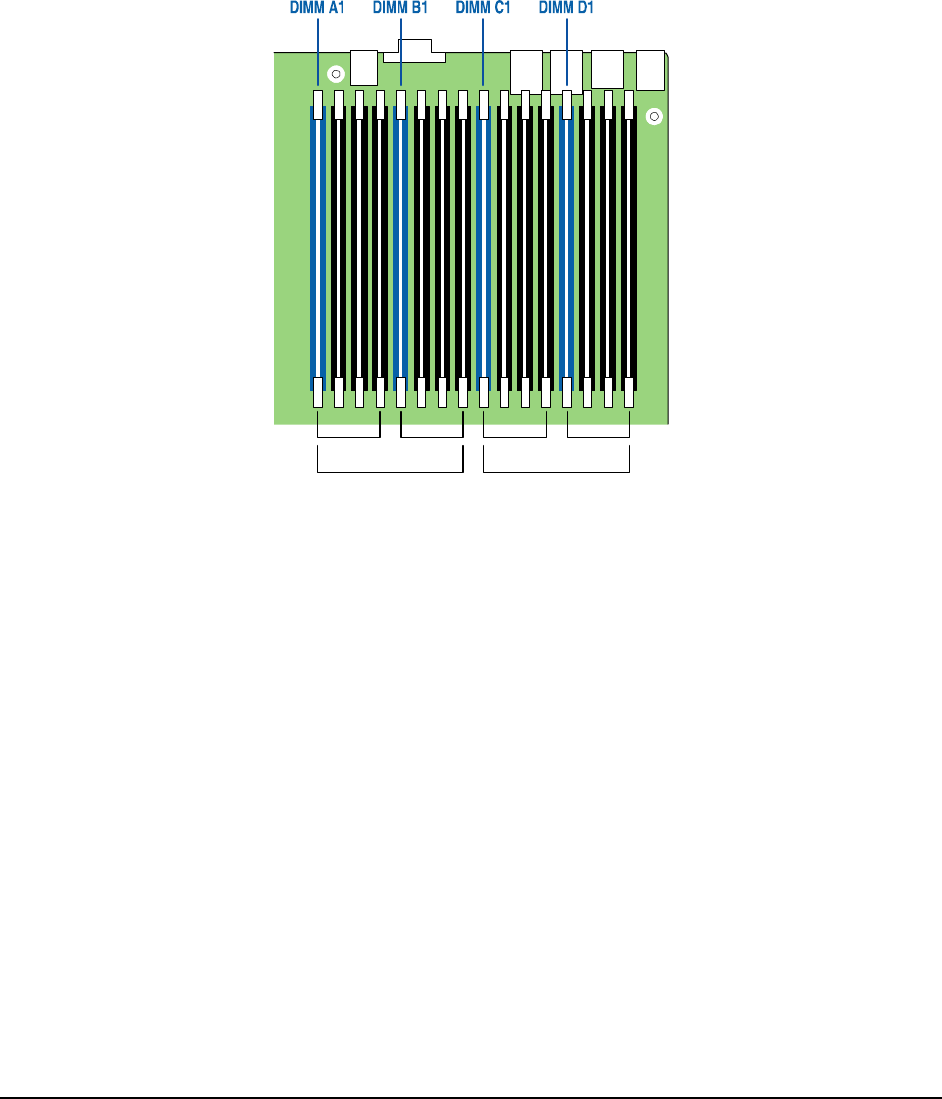

3.2.3.4 Memory upgrades

The minimum memory upgrade increment is two DIMMs per branch. The DIMMs must cover the

same slot position on both channels. DIMMs pairs must be identical with respect to size, speed,

and organization. DIMMs that cover adjacent slot positions do not need to be identical.

When adding two DIMMs to the configuration shown in Figure 8, the DIMMs should be

populated in DIMM slots C1 and D1 as shown in the following figure:

AF002166

Branch 0 Branch 1

Channel A Channel D

Channel B Channel C

Figure 9. Recommended Four-DIMM Configuration

Functionally, DIMM slots A2 and B2 could also be populated instead of DIMM slots C1 and D1.

However, the system does not achieve equivalent performance. The above figure shows the

supported DIMM configuration that is recommended because it allows both memory branches

from the MCH to operate independently and simultaneously. Memory bandwidth is doubled

when both branches operate in parallel.

3.2.3.5 ECC Code Support

When branches operate in the dual-channel mode, the MCH supports the 18 device DRAM

failure correction code (SDDC aka SECC) option for FBD. As applied by the MCH, this code has

the following properties:

Correction of any x4 or x8 DRAM device failure

Detection of 99.986% of all single bit failures that occur in addition to a x8 DRAM failure.

The MCH detects a series of failures on a specific DRAM and uses this information in

addition to the information provided by the code to achieve 100% detection of these

cases.

Detection of all two wire faults on the DIMMs. This includes any pair of single bit errors.

Detection of all permutations of 2 x4 DRAM failures.