Technical Product Specification

Appendix D: POST Code LED Decoder Intel

®

Server Board S2600WP TPS

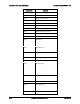

Table 108. MRC Progress Codes

Progress Code

Main Sequence

Subsequences/Subfunctions

0xB0

Detect DIMM population

—n/a—

0xB1

Set DDR3 frequency

—n/a—

0xB2

Gather remaining SPD data

—n/a—

0xB3

Program registers on the memory controller level

—n/a—

0xB4

Evaluate RAS modes and save rank information

—n/a—

0xB5

Program registers on the channel level

—n/a—

0xB6

Perform the JEDEC defined initialization

sequence

—n/a—

0xB7

Train DDR3 ranks

—n/a—

0x01

Read DQ/DQS training

0x02

Receive Enable training

0x03

Write Leveling training

0x04

Write DQ/DQS training

0x05

DDR channel training done

0xB8

Initialize CLTT/OLTT

—n/a—

0xB9

Hardware memory test and init

—n/a—

0xBA

Execute software memory init

—n/a—

0xBB

Program memory map and interleaving

—n/a—

0xBC

Program RAS configuration

—n/a—

0xBF

MRC is done

—n/a—

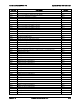

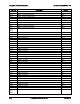

Table 109. POST Progress Codes

Progress Code

Description

SEC Phase

0x01 First POST code after CPU reset

0x02 Microcode load begin

0x03 CRAM initialization begin

0x04 Pei Cache When Disabled

0x05 SEC Core At Power On Begin

0x06

Early CPU initialization during Sec

Phase

0x07 Early SB initialization during Sec Phase

Intel order number G44057-007 Revision 1.6

210