Technical Product Specification

Appendix D: POST Code Diagnostic LED Decoder Intel® Server Boards S4600LH2/T2 TPS

Revision 2.0

234

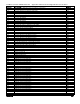

Checkpoint

Diagnostic LED Decoder

Description

1 = LED On, 0 = LED Off

Upper Nibble

Lower Nibble

MSB

LSB

8h

4h

2h

1h

8h

4h

2h

1h

LED

#7

#6

#5

#4

#3

#2

#1

#0

B6h

1

0

1

1

0

1

1

0

Perform the JEDEC defined initialization sequence

B7h

1

0

1

1

0

1

1

1

Train DDR3 ranks

B8h

1

0

1

1

1

0

0

0

Initialize CLTT/OLTT

B9h

1

0

1

1

1

0

0

1

Hardware memory test and init

BAh

1

0

1

1

1

0

1

0

Execute software memory init

BBh

1

0

1

1

1

0

1

1

Program memory map and interleaving

BCh

1

0

1

1

1

1

0

0

Program RAS configuration

BFh

1

0

1

1

1

1

1

1

MRC is done

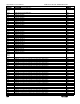

Memory Initialization at the beginning of POST includes multiple functions, including: discovery, channel

training, validation that the DIMM population is acceptable and functional, initialization of the IMC and

other hardware settings, and initialization of applicable RAS configurations.

When a major memory initialization error occurs and prevents the system from booting with data

integrity, a beep code is generated, the MRC will display a fatal error code on the diagnostic LEDs, and a

system halt command is executed. Fatal MRC error halts do NOT change the state of the System Status

LED, and they do NOT get logged as SEL events. The following table lists all MRC fatal errors that are

displayed to the Diagnostic LEDs.

Table 73. MRC Fatal Error Codes

Checkpoint

Diagnostic LED Decoder

Description

1 = LED On, 0 = LED Off

Upper Nibble

Lower Nibble

MSB

LSB

8h

4h

2h

1h

8h

4h

2h

1h

LED

#7

#6

#5

#4

#3

#2

#1

#0

MRC Fatal Error Codes

E8h

1 1 1 0 1 0 0 0

No usable memory error

01h = No memory was detected from SPD read, or invalid config that

causes no operable memory.

02h = Memory DIMMs on all channels of all sockets are disabled due to

hardware memtest error.

3h = No memory installed. All channels are disabled.

E9h

1 1 1 0 1 0 0 1

Memory is locked by Intel Trusted Execution Technology and is

inaccessible