Specification Update

Table Of Contents

Intel

®

E7520 Memory Controller Hub (MCH) Specification Update 7

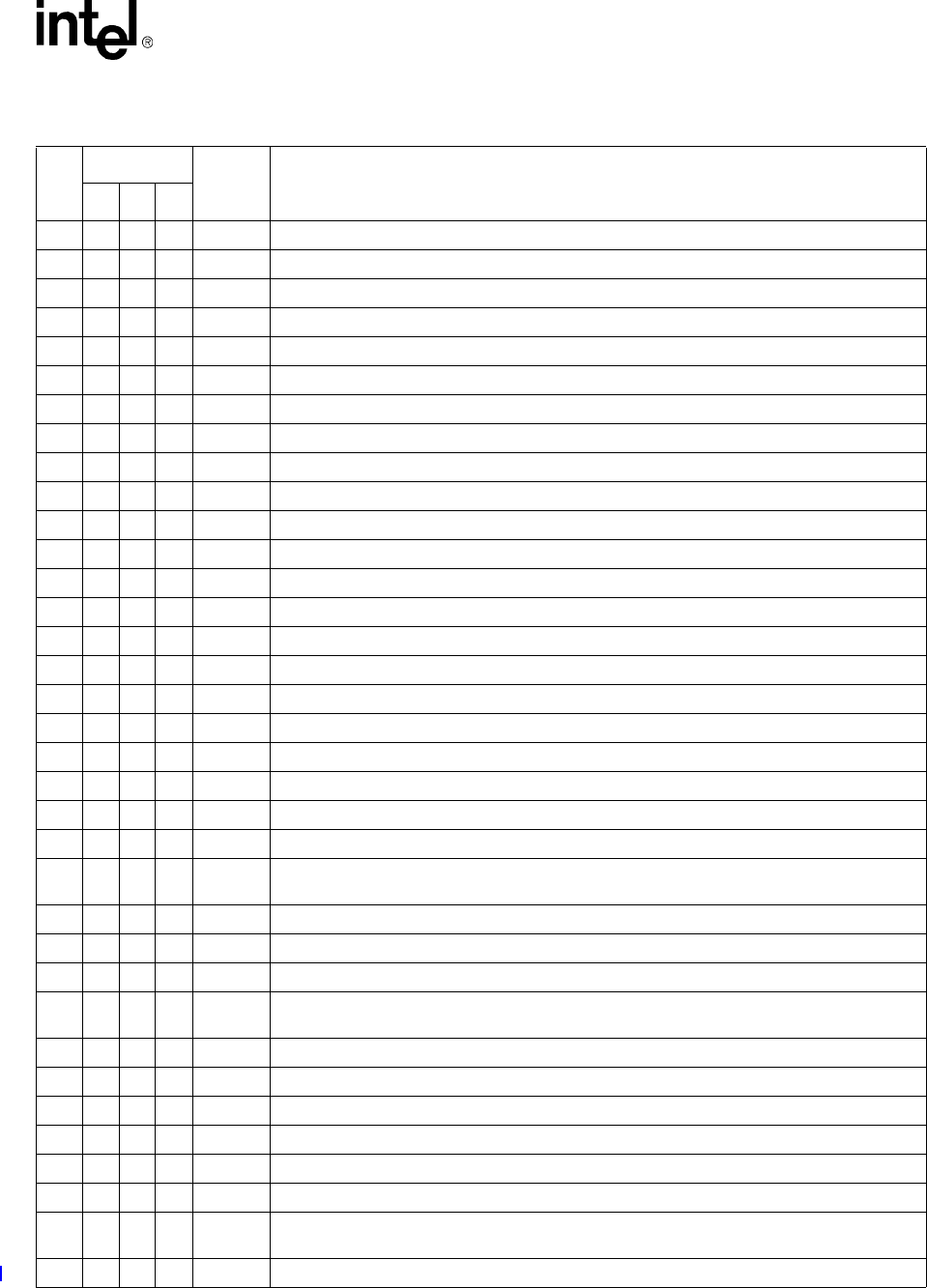

Summary Table of Changes

Errata

No.

Stepping

Status ERRATA

C1 C2 C4

1 XXXNo Fix DMA channel source address checking error

2 XXXNo Fix Data corruption after an illegal front side bus configuration Write

3 XXXNo Fix Improper ECC and Memory Initialization while in Symmetric mode

4 XXXNo Fix Single Channel ECC Error Injection issue

5 XXXNo Fix PCI Express* add-in card presence detect state misreported

6 XXXNo Fix Incorrect PCI Express Link/Lane numbers driven in degraded link

7 XXXNo Fix PCI Express Compliance Mode issue

8 XXXNo fix PCI Express Hot-Plug MSI interrupt issue

9 XXXNo Fix PCI Express link training failures on hot reset

10 XXXNo Fix Subsystem Identification and Subsystem Vendor Identification register issue

11 XXXNo Fix MCH responds with illegal access on the Hub Interface for 32 GB configurations

12 XXXNo Fix MCH hang on PCI Express enhanced configurations to non-existent devices causes hang

13 XXXNo Fix Spurious errors logged during link training events

14 XXXNo Fix DDR2 write offset issue

15 XXXNo Fix DMA MSI interrupt issue

16 XXXNo Fix SEC and DED error counters aliased in mirror mode

17 XXXNo Fix HiLoCS bit not readable in memory error address registers

18 XXXNo Fix MCH transitions from Polling.Active prematurely

19 XXXNo Fix Non-fatal completion timeout errors observed on PCI Express devices

20 XXXNo Fix SEC errors may be reported on opposite channel’s error registers in memory mirroring mode

21 XXXNo Fix MCH fails to train when non-TS1/TS2 training sequences are received

22 XXXNo Fix DIMM sparing issue with demand scrub enabled

23 XXXNo Fix Configuration transaction may be ignored in MCH when Configuration Request Retry Status is

enabled in PCI Express to PCI/PCI-X bridges

24 XXXNo Fix PCI Express Hot-Plug indicator blink causes extra SMBus write

25 XXXNo Fix PCI Express x4, x8 links may train down to lower width

26 XXXNo Fix SKP ordered set may not be sent within required interval

27 XXXNo Fix END symbol omitted from the last PM_Request_Ack DLLP while entering L2 state on x1 PCI

Express link

28

X X Plan Fix System hang may occur when entering S4 and S5 power states

29 X X Plan Fix Transposed interrupt messages across Hub Interface

30 XXXNo Fix Completion timeout errors in the presence of heavy PCI Express peer-to-peer traffic

31 XXXNo Fix SMBDAT and SMBCLK signals pulled down in S5

32 XXXNo Fix Multiple PCI Express protocol errors may result in fatal receiver overflow

33 XXXNo Fix System marginalities may result in spurious link-down error events on power state changes

34 XXXNo Fix Possible loss of Hot-swap Power Fault Event in dual PCI Express Hot-swap port

configurations

35 XXXFixed Memory initialization may fail at low temperatures