Desktop 4th Generation Specification Sheet

Table Of Contents

- Contents

- Revision History

- 1.0 Introduction

- 2.0 Interfaces

- 3.0 Technologies

- 3.1 Intel® Virtualization Technology (Intel® VT)

- 3.2 Intel® Trusted Execution Technology (Intel® TXT)

- 3.3 Intel® Hyper-Threading Technology (Intel® HT Technology)

- 3.4 Intel® Turbo Boost Technology 2.0

- 3.5 Intel® Advanced Vector Extensions 2.0 (Intel® AVX2)

- 3.6 Intel® Advanced Encryption Standard New Instructions (Intel® AES-NI)

- 3.7 Intel® Transactional Synchronization Extensions - New Instructions (Intel® TSX-NI)

- 3.8 Intel® 64 Architecture x2APIC

- 3.9 Power Aware Interrupt Routing (PAIR)

- 3.10 Execute Disable Bit

- 3.11 Supervisor Mode Execution Protection (SMEP)

- 4.0 Power Management

- 4.1 Advanced Configuration and Power Interface (ACPI) States Supported

- 4.2 Processor Core Power Management

- 4.3 Integrated Memory Controller (IMC) Power Management

- 4.4 PCI Express* Power Management

- 4.5 Direct Media Interface (DMI) Power Management

- 4.6 Graphics Power Management

- 5.0 Thermal Management

- 5.1 Desktop Processor Thermal Profiles

- 5.2 Thermal Metrology

- 5.3 Fan Speed Control Scheme with Digital Thermal Sensor (DTS) 1.1

- 5.4 Fan Speed Control Scheme with Digital Thermal Sensor (DTS) 2.0

- 5.5 Processor Temperature

- 5.6 Adaptive Thermal Monitor

- 5.7 THERMTRIP# Signal

- 5.8 Digital Thermal Sensor

- 5.9 Intel® Turbo Boost Technology Thermal Considerations

- 6.0 Signal Description

- 6.1 System Memory Interface Signals

- 6.2 Memory Reference and Compensation Signals

- 6.3 Reset and Miscellaneous Signals

- 6.4 PCI Express*-Based Interface Signals

- 6.5 Display Interface Signals

- 6.6 Direct Media Interface (DMI)

- 6.7 Phase Locked Loop (PLL) Signals

- 6.8 Testability Signals

- 6.9 Error and Thermal Protection Signals

- 6.10 Power Sequencing Signals

- 6.11 Processor Power Signals

- 6.12 Sense Signals

- 6.13 Ground and Non-Critical to Function (NCTF) Signals

- 6.14 Processor Internal Pull-Up / Pull-Down Terminations

- 7.0 Electrical Specifications

- 8.0 Package Mechanical Specifications

- 9.0 Processor Ball and Signal Information

• AC tolerances for all DC rails include dynamic load currents at switching

frequencies up to 1 MHz.

Voltage and Current Specifications

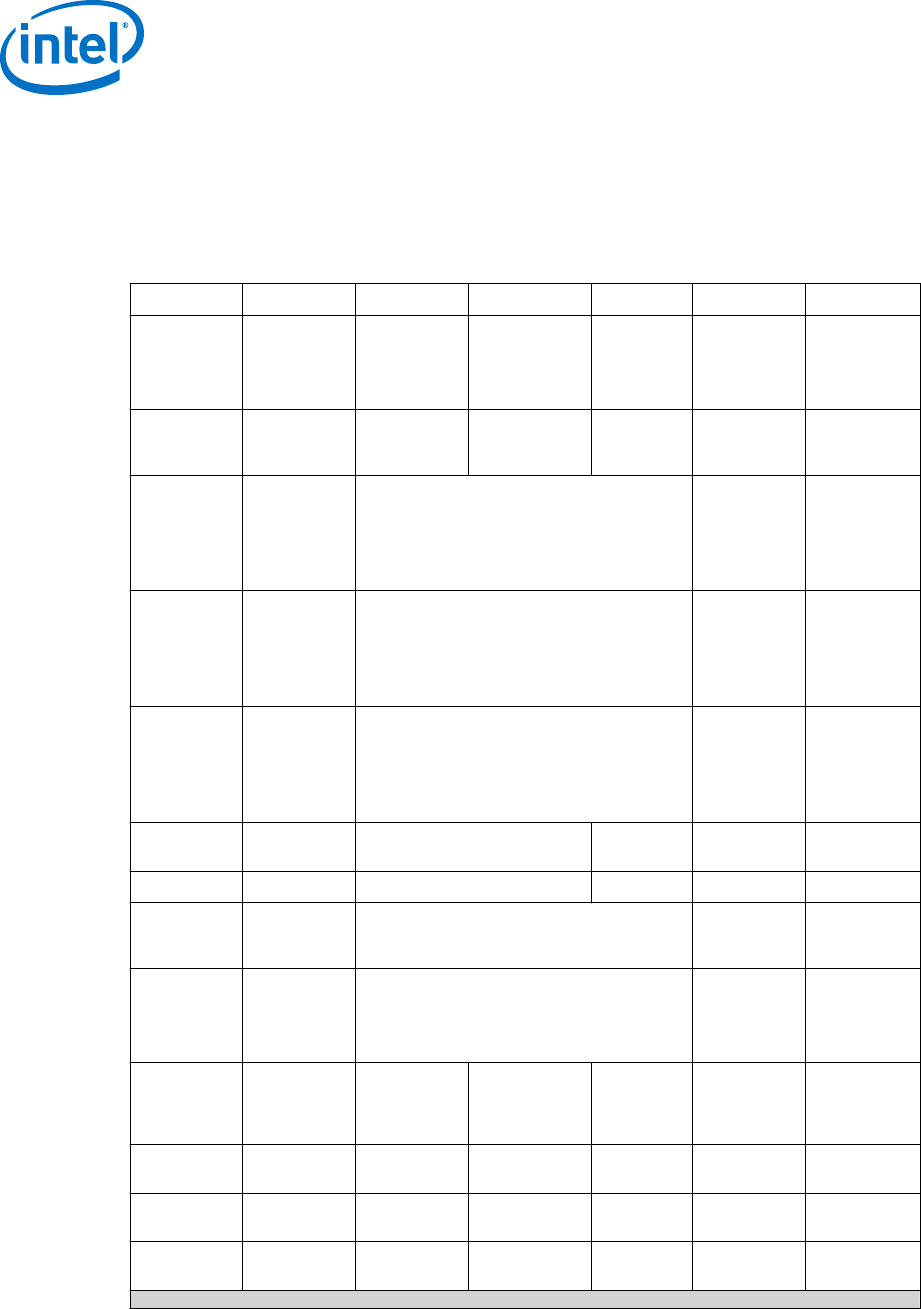

Table 47. Processor Core Active and Idle Mode DC Voltage and Current Specifications

Symbol Parameter Min Typ Max Unit Note

1

Operational

VID

VID Range 1.65

2013D: 1.75

2013C: 1.75

2013B: 1.75

2013A: 1.75

1.86 V 2

Idle VID

(package

C6/C7)

VID Range 1.5 1.6 1.65 V 2

R_DC_LL

Loadline

slope within

the VR

regulation

loop

capability

2013D PCG: -1.5

2013C PCG: -1.5

2013B PCG: -1.5

2013A PCG: -1.5

mΩ 3, 5, 6, 8

R_AC_LL

Loadline

slope in

response to

dynamic load

increase

events

2013D PCG: -2.4

2013C PCG: -2.4

2013B PCG: -2.4

2013A PCG: -2.4

mΩ —

R_AC_LL_OS

Loadline

slope in

response to

dynamic load

release

events

2013D PCG: -3.0

2013C PCG: -3.0

2013B PCG: -3.0

2013A PCG: -3.0

mΩ —

T_OVS

Overshoot

time

500 uS

V_OVS Overshoot 50 mV

V

CC

TOB

V

CC

Tolerance

Band

± 20 (PS0, PS1, PS2, PS3) mV 3, 5, 6, 7, 8

V

CC

Ripple

Ripple ± 10 (PS0)

± 15 (PS1)

+50/-15 (PS2)

+60/-15 (PS3)

mV 3, 5, 6, 7, 8

V

CC,BOOT

Default V

CC

voltage for

initial power

up

— 1.70 — V —

I

CC

2013D PCG

I

CC

— — 95 A 4, 8

I

CC

2013C PCG

I

CC

— — 75 A 4, 8

I

CC

2013B PCG

I

CC

— — 58 A 4, 8

continued...

7.8

Processor—Electrical Specifications

Desktop 4th Generation Intel

®

Core

™

Processor Family, Desktop Intel

®

Pentium

®

Processor Family, and Desktop Intel

®

Celeron

®

Processor Family

Datasheet – Volume 1 of 2 December 2013

98 Order No.: 328897-004