Desktop 4th Generation Specification Sheet

Table Of Contents

- Contents

- Revision History

- 1.0 Introduction

- 2.0 Interfaces

- 3.0 Technologies

- 3.1 Intel® Virtualization Technology (Intel® VT)

- 3.2 Intel® Trusted Execution Technology (Intel® TXT)

- 3.3 Intel® Hyper-Threading Technology (Intel® HT Technology)

- 3.4 Intel® Turbo Boost Technology 2.0

- 3.5 Intel® Advanced Vector Extensions 2.0 (Intel® AVX2)

- 3.6 Intel® Advanced Encryption Standard New Instructions (Intel® AES-NI)

- 3.7 Intel® Transactional Synchronization Extensions - New Instructions (Intel® TSX-NI)

- 3.8 Intel® 64 Architecture x2APIC

- 3.9 Power Aware Interrupt Routing (PAIR)

- 3.10 Execute Disable Bit

- 3.11 Supervisor Mode Execution Protection (SMEP)

- 4.0 Power Management

- 4.1 Advanced Configuration and Power Interface (ACPI) States Supported

- 4.2 Processor Core Power Management

- 4.3 Integrated Memory Controller (IMC) Power Management

- 4.4 PCI Express* Power Management

- 4.5 Direct Media Interface (DMI) Power Management

- 4.6 Graphics Power Management

- 5.0 Thermal Management

- 5.1 Desktop Processor Thermal Profiles

- 5.2 Thermal Metrology

- 5.3 Fan Speed Control Scheme with Digital Thermal Sensor (DTS) 1.1

- 5.4 Fan Speed Control Scheme with Digital Thermal Sensor (DTS) 2.0

- 5.5 Processor Temperature

- 5.6 Adaptive Thermal Monitor

- 5.7 THERMTRIP# Signal

- 5.8 Digital Thermal Sensor

- 5.9 Intel® Turbo Boost Technology Thermal Considerations

- 6.0 Signal Description

- 6.1 System Memory Interface Signals

- 6.2 Memory Reference and Compensation Signals

- 6.3 Reset and Miscellaneous Signals

- 6.4 PCI Express*-Based Interface Signals

- 6.5 Display Interface Signals

- 6.6 Direct Media Interface (DMI)

- 6.7 Phase Locked Loop (PLL) Signals

- 6.8 Testability Signals

- 6.9 Error and Thermal Protection Signals

- 6.10 Power Sequencing Signals

- 6.11 Processor Power Signals

- 6.12 Sense Signals

- 6.13 Ground and Non-Critical to Function (NCTF) Signals

- 6.14 Processor Internal Pull-Up / Pull-Down Terminations

- 7.0 Electrical Specifications

- 8.0 Package Mechanical Specifications

- 9.0 Processor Ball and Signal Information

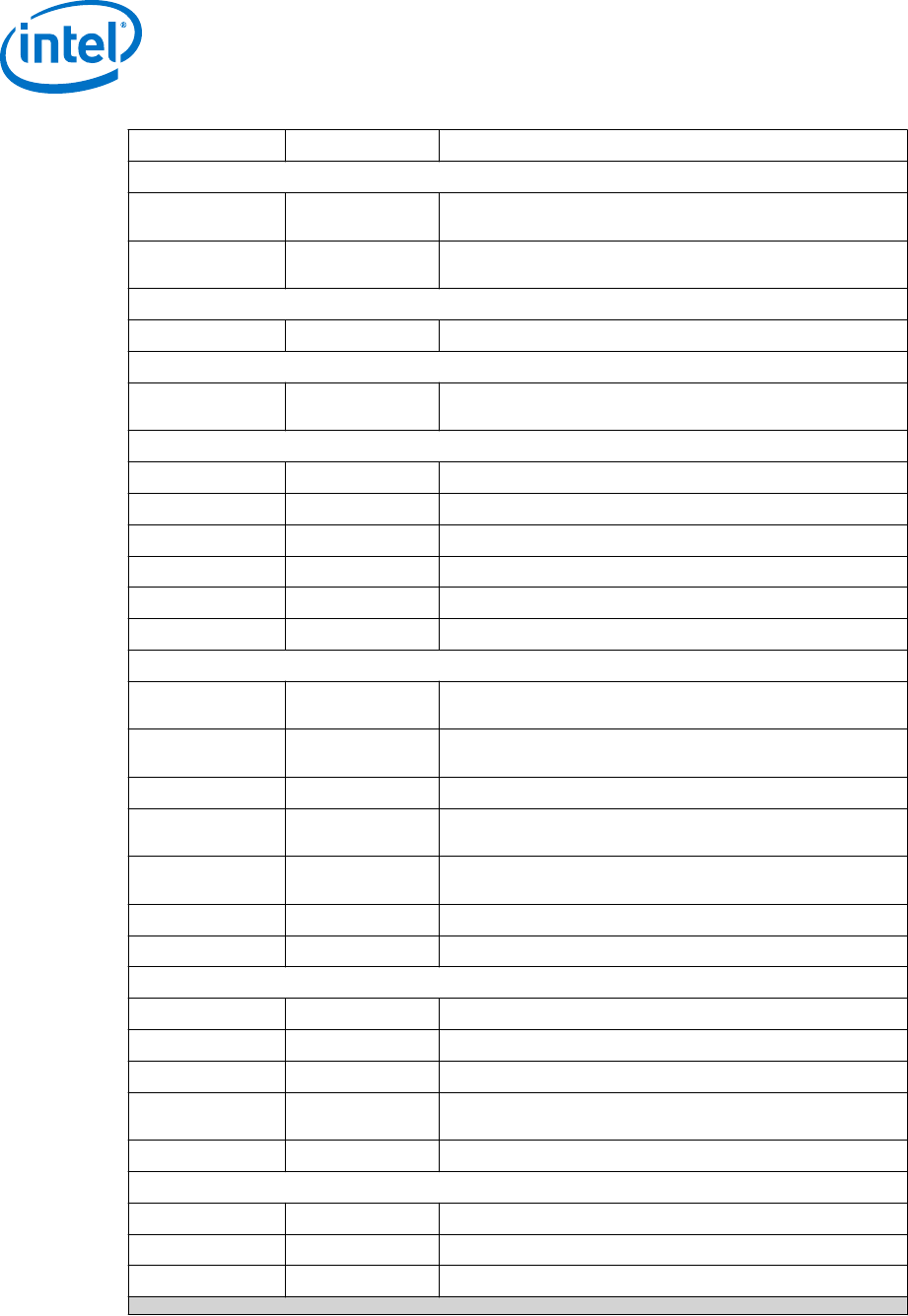

Signal Group Type Signals

DDR3 / DDR3L Data Signals

2

Single ended DDR3/DDR3L Bi-

directional

SA_DQ[63:0], SB_DQ[63:0]

Differential DDR3/DDR3L Bi-

directional

SA_DQSP[7:0], SA_DQSN[7:0], SB_DQSP[7:0], SB_DQSN[7:0]

DDR3 / DDR3L Compensation

Analog Input SM_RCOMP[2:0]

DDR3 / DDR3L Reference Voltage Signals

DDR3/DDR3L

Output

SM_VREF, SA_DIMM_VREFDQ, SB_DIMM_VREFDQ

Testability (ITP/XDP)

Single ended CMOS Input TCK, TDI, TMS, TRST#

Single ended GTL TDO

Single ended Output DBR#

Single ended GTL BPM#[7:0]

Single ended GTL PREQ#

Single ended GTL PRDY#

Control Sideband

Single ended GTL Input/Open

Drain Output

PROCHOT#

Single ended Asynchronous

CMOS Output

THERMTRIP#, IVR_ERROR

Single ended GTL CATERR#

Single ended Asynchronous

CMOS Input

PM_SYNC,RESET#, PWRGOOD, PWR_DEBUG#

Single ended Asynchronous Bi-

directional

PECI

Single ended GTL Bi-directional CFG[19:0]

Single ended Analog Input SM_RCOMP[2:0]

Voltage Regulator

Single ended CMOS Input VR_READY

Single ended CMOS Input VIDALERT#

Single ended Open Drain Output VIDSCLK

Single ended GTL Input/Open

Drain Output

VIDSOUT

Differential Analog Output VCC_SENSE, VSS_SENSE

Power / Ground / Other

Single ended Power VCC, VDDQ

Ground VSS, VSS_NCTF

3

No Connect RSVD, RSVD_NCTF

continued...

Processor—Electrical Specifications

Desktop 4th Generation Intel

®

Core

™

Processor Family, Desktop Intel

®

Pentium

®

Processor Family, and Desktop Intel

®

Celeron

®

Processor Family

Datasheet – Volume 1 of 2 December 2013

96 Order No.: 328897-004