User's Manual

Table Of Contents

- 1.0 General Description

- 2.0 Introduction

- 3.0 Quick-Start Checklist

- 4.0 Optional Configurations

- 5.0 LEDs

- 6.0 Board Schematics

- Figure 4. LXD9785 PQFP MII Demo Board Power (Fiber Board Revision A2)

- Figure 5. Control

- Figure 6. MII Ports 0 and 1

- Figure 7. MII Ports 2 and 3

- Figure 8. MII Ports 4 and 5

- Figure 9. MII Ports 6 and 7

- Figure 10. Fiber Ports 0 and 1

- Figure 11. Fiber Ports 2 and 3

- Figure 12. Fiber Ports 4 and 5

- Figure 13. Fiber Ports 6 and 7

- Figure 14. Caps

- Figure 15. SS-SMII to MII ALTERA

- Figure 16. Clock Distribution

- Figure 17. Inter-Frame Status LEDs

- Figure 18. Logic Analyzer

- Figure 19. MDIO0 and MDC0 Fix

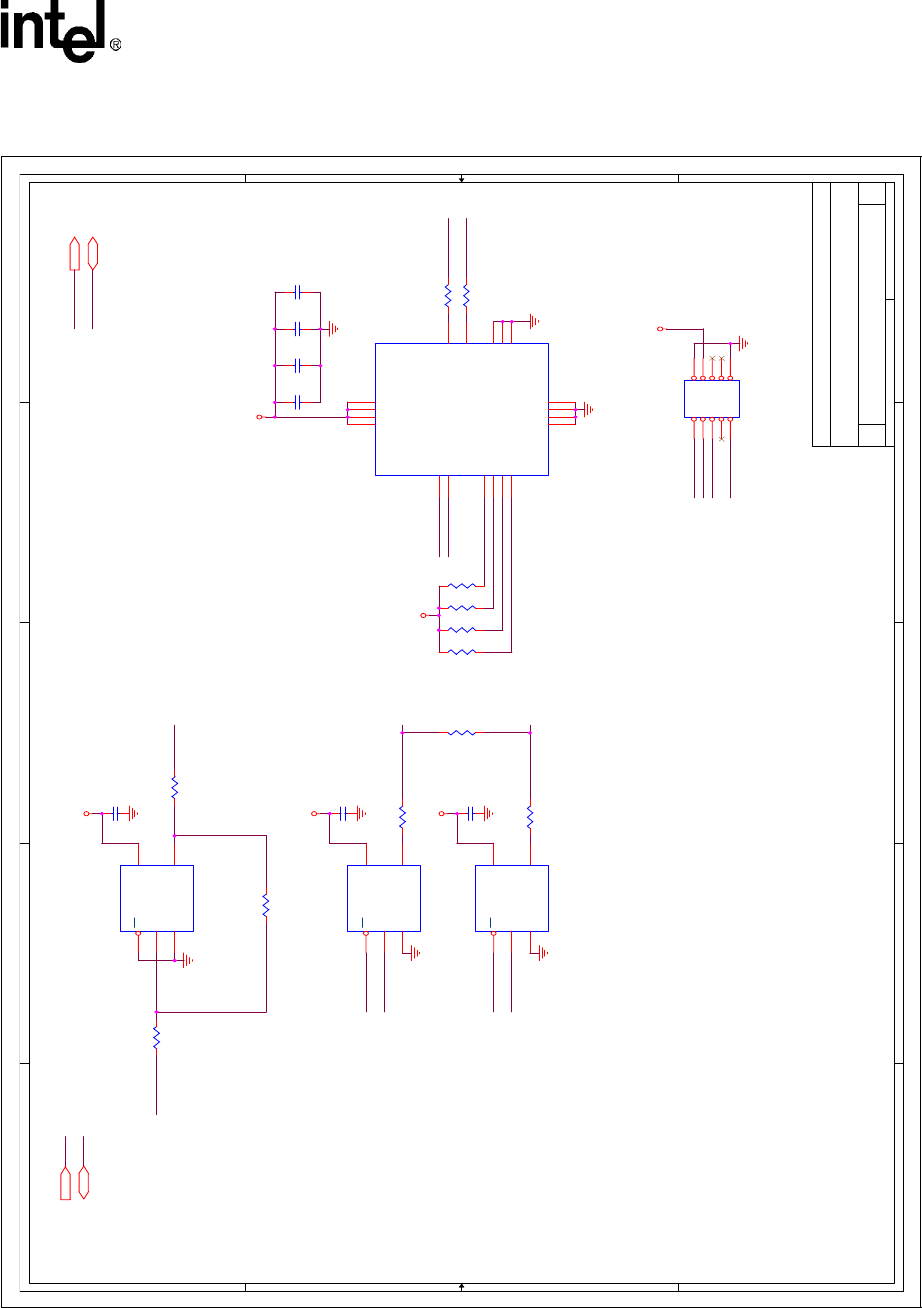

- Figure 20. MDIO1 and MDC1 Fix

- 7.0 Bill of Materials

LXD9785 PQFP Demo Board with FPGA for SS-SMII (Fiber)-to-MII Conversion

Development Kit Manual 35

Document #: 249323

Revision #: 003

Rev. Date: January 24, 2002

Figure 20. MDIO1 and MDC1 Fix

A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

MDIO1 & MDC1 FIX A2

LXD9785 SS/SMII MII FX DV BOARD

B

18 18Wednesday, February 21, 2001

Title

Size Document Number Rev

Date: Sheet

of

MDC1_FIX

MDC1

PLD1_OE0

PLD1_OE1

PLD1_OE0

PLD1_OE1

MDC1

MDIO1_FIX

MDIO1_FIX

MDIO1

MDIO1

MDIO1_FIX

MDIO1

MDC1

MDIO1

PLD1_TDO

PLD1_TCK

PLD1_TMS

PLD1_TDI

PLD1_TDO

PLD1_TCK

PLD1_TMS

PLD1_TDI

MDC1_FIX

MDC1_FIX3

MDC1 3

MDIO1 3

MDIO1_FIX3

GND

GND

GND

GND

GND

GND

GND

GND

GND

VCC_EXT

GND

VCC_EXT

VCC_EXT

VCC_MDIO

VCC_MDIO

VCC_MDIO

R622

1K

R621

1K

R620

1K

R619

1K

U40

NC7SZ125M5

1

2

3 4

5

OE

A

GND Y

VCC

U41

NC7SZ125M5

1

2

3 4

5

OE

A

GND Y

VCC

U43

NC7SZ125M5

1

2

3 4

5

OE

A

GND Y

VCC

R616 50 1%

R617 50 1%

C358

0.1uF

U42

EPM7032AETC44-4

1

4

7

9

17

18

20

24

26

29

32

36

37

38

39

40

41

42

16

TDI

GNDIO

TMS

VCCIO

VCCINT

OUT_ENABLE1

OUT_ENABLE0

GNDIO

TCK

VCCIO

TDO

GNDINT

MDC

INPUT1

INPUT2

INPUT3

VCCINT

MDIO

GNDINT

C357

0.01uF

R615 0 OHMS

C355

0.01uF

R729 0 OHMS

C356

0.1uF

R730 0 OHMS

R618 50 1%

R738

0 OHMS

R623 50 1%

C352

0.01uF

JP21

HEADER 5X2

12

34

56

78

910

C354

0.01uF

C353

0.01uF