32-Bit High-Performance Superscalar Processor Data Sheet

80960HA/HD/HT

80 Datasheet

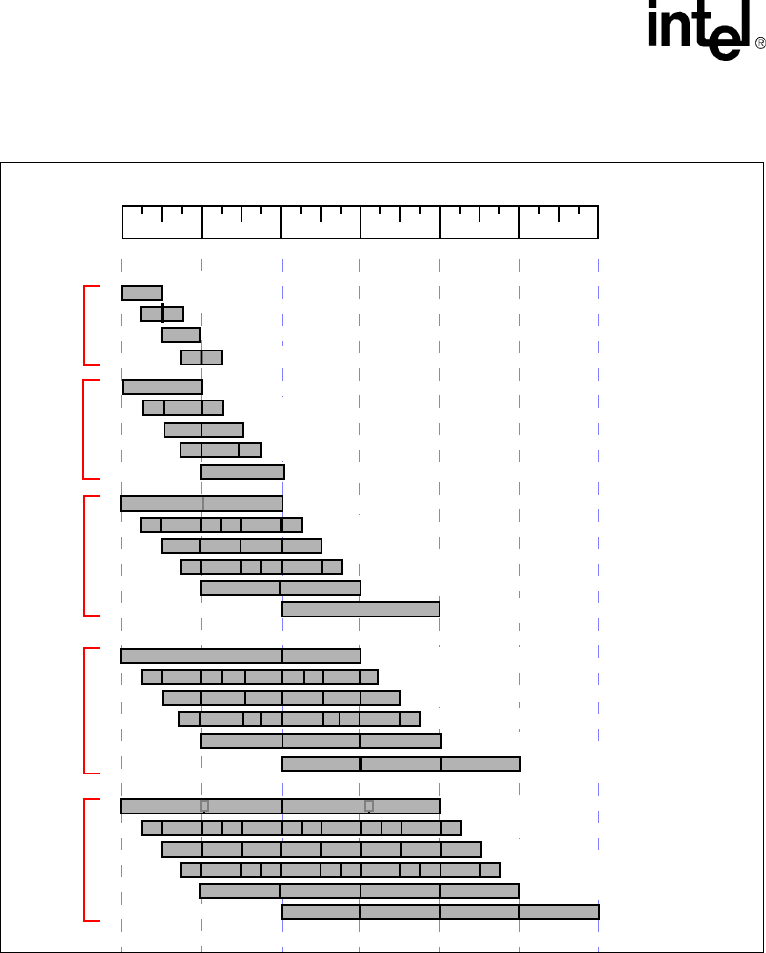

Figure 56. A Summary of Aligned and Unaligned Transfers for 16-Bit Bus

04 812162024

01234 56

Byte Offset

Word Offset

Double Word

16-Bit Bus

Triple Word

16-Bit Bus

Quad Word

16-Bit Bus

Short

16-Bit Bus

Word

16-Bit Bus

Short

Four Short Burst

(Byte, Short, Byte) *2

(Short) *4

(Byte, Short, Byte)*2

Four Short Burst, Two Short Burst

(Byte, Short, Byte) *3

(Short) *6

(Byte, Short, Byte) *3

(Two Short Burst) *3

(Two Short Burst) *3

(Four Short Burst)*2

(Byte, Short, Byte) *4

(Short) *8

(Two Short Burst)*4

(Two Short Burst) *4

Short

Byte, Byte

(Byte, Short, Byte) *4

Four Short Burst

Two Short Burst

Byte, Short, Byte

(Short)*2

Two Short Burst

Byte, Short, Byte

Byte, Byte

(Two Short Burst)*2